How to set the PMBus assignment in the Intel® Quartus Prime® Software

Success! Subscription added.

Success! Subscription removed.

Sorry, you must verify to complete this action. Please click the verification link in your email. You may re-send via your profile.

- Intel Community

- Intel Community Knowledge Base

- Product Support Forums Knowledge Base

- FPGA Knowledge Base

- FPGA Wiki

- How to set the PMBus assignment in the Intel® Quartus Prime® Software

How to set the PMBus assignment in the Intel® Quartus Prime® Software

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report Inappropriate Content

How to set the PMBus assignment in the Intel® Quartus Prime® Software for Intel® Stratix® 10 FPGA / Intel Agilex® FPGA

Intel® Stratix® 10 FPGA and Intel Agilex® FPGA with SmartVID feature need to set the PMBus assignment properly in Intel® Quartus® Prime Software. Otherwise, you would observe the configuration failure with an error message with SmartVID content.

To properly set the assignment, you could follow below steps:

1. Pin Assignment

Assign the SDM bank pins following your board design. You can find these settings in the path: Quartus Prime Pro > Assignments > Device > Device and Pin Options > Configuration > Configuration Pin Options.

If you are using the FPGA with the SmartVID feature, the PWRMGT_SCL and PWRMGT_SDA are mandatory, and you also need to confirm these two pins are properly connected to the Voltage Regulator (VR) on your board. Most VR PMBus interfaces are designed as 3.3V, and you may need to use a level shifter to bridge the 1.8V SDM I/O and VR PMBus port.

2. Power Management and VID settings

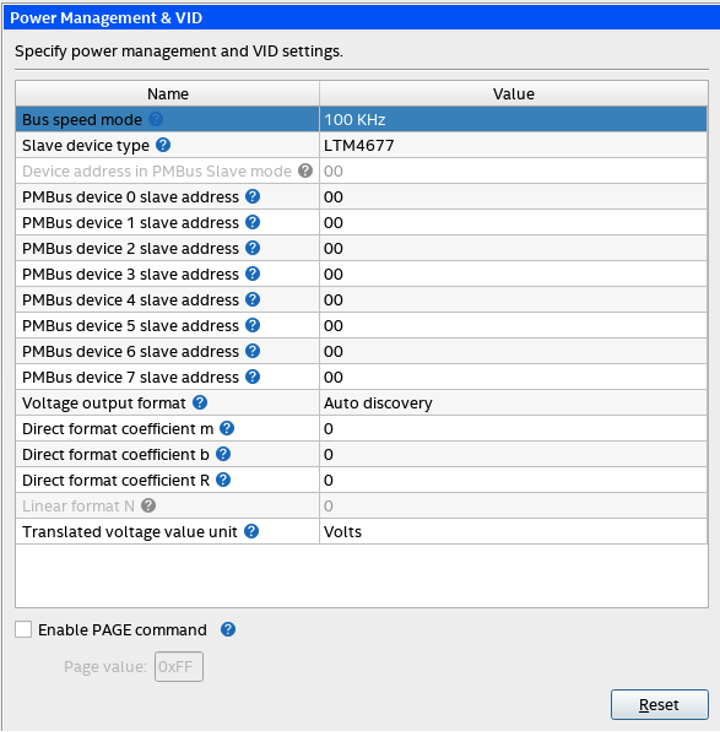

Go to the below window, and you will see the default setting like below. You need to set these options following the VR and your board.

Quartus Prime Pro > Assignments > Device > Device and pin Options > Power Management & VID

3. Bus speed mode

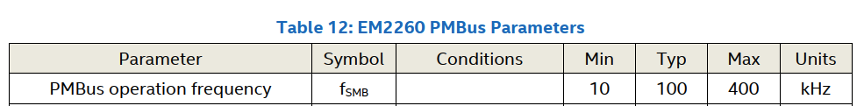

This option should be set to follow the VR specification. It would take Enpirion* EM2260 as an example, and you could find the specification in the datasheet from your VR’s vendor.

For EM2260, The PMBus operation frequency is 100 kHz typical and supports the minimal to maximum frequency from 10 k to 400 kHz.

So, for this option, you can set the Bus speed mode to 100 kHz.

4. Slave device type

In Intel Quartus Prime Pro Software, you have preset some popular VR mode in this option for your convenient choice. But if your VR is out of the preset list, you should choose the Other.

For EM2260, in this example, you set this option to EM22XX.

5. PMBus device slave address

The PMBus device slave address depends on the VR’s setting and your board scheme. Generally, the VR could set the address by an external resistor with different values. You should select this option following your board design. Here you take 55 as an example.

6. Voltage output format

The voltage output format should be set following the VR, and different VR model would have different output mode.

For EM2260, it supports linear mode following the datasheet mentioned.

For EM2260 in this example, you set this option to Linear.

7. Translate voltage value unit

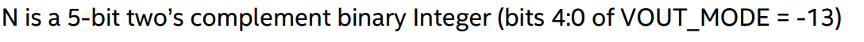

Like step 6, you also need to find this parameter in the VR’s datasheet. For EM2260, you could see the N equals -13. You set the -13 for this option in this example.

8. Enable PAGE command

If your VR has more than one rail output, you should control all the rails for FPGA at the same time. Most of the time, you have one dedicated VR for the FPGA VCC power rail. You could set it as 0xFF to let SDM control all the available VR output rail.

For EM2260, you take 0xFF as an example.

9. Compilation

With all the settings complete, you can compile your design and configure the image file to FPGA.

10. Known Issues

For a known issue of the Intel® Stratix® 10 FPGA PMBus setting on Quartus Prime Pro Software version 20.4 and prior, you could refer to

https://www.intel.com/content/altera-www/global/en_us/index/support/support-resources/knowledge-base/tools/2021/can-the-sdm-firmware-cause-an-external-voltage-regulator-to-appl.html

For more PMBus and configuration information, you could refer to

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/stratix-10/ug-s10-config.pdf

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/agilex/ug-ag-config.pdf

Notices & Disclaimers

Intel technologies may require enabled hardware, software, or service activation.

No product or component can be absolutely secure.

Your costs and results may vary.

Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries.

The products described may contain design defects or errors known as errata, which may cause the product to deviate from published specifications. Current characterized errata are available on request.

The Intel logo, and Intel Agilex are trademarks of Intel Corporation or its subsidiaries

2021-06-27

Fan Hui Dong

Community support is provided Monday to Friday. Other contact methods are available here.

Intel does not verify all solutions, including but not limited to any file transfers that may appear in this community. Accordingly, Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade.

For more complete information about compiler optimizations, see our Optimization Notice.