- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ,

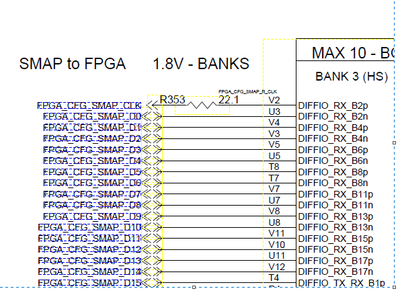

We are using 10M08SAU324I7G chipset in our design. We are using SMAP interface to Program the FPGA(XCKU5P series) from CPLD.

Below are the Pins are used for SMAP interface. In our design, we have routed 15inch traces between FPGA and CPLD due to dense board. For this we have simulated and it pass only "18_RIO_R50C" model.

Is it possible to configure this "18 RIO R50C" model for the pins listed below?Please advise and share if any guidelines.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

You can confirm this by referring to MAX10 ibis model.

Download link : https://cdrdv2.intel.com/v1/dl/getContent/674923?explicitVersion=true

regards,

Farabi

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I’m glad that your question has been addressed, I now transition this thread to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

rgards,

Farabi

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page