- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I could compile and synthesize the counter example correctly with the HLS compiler. I also added my newly created IP to my existing design in Platform Designer. But how can I generate the call and return signals now to run the IP block continuously?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

May I know what is the meaning of "call and and return signal" here?

Based on my understanding, "call and return signal" is transfer data or read data to the new IP block, am I right? If yes, you may need to connect avalon mm /avalon st/ conduit, the connection inside the Platform Designer is depend on your application.

For more information about avalon interface, you may need to refer the document as link below:

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/manual/mnl_avalon_spec.pdf

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for this helpful information.

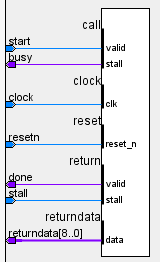

I'm not sure if "call and return signal" is transfer data or read data of the IP block. I can't find any documentation on these signals and how they are generated by a function call by value in HLS. Are these signals generated just for the testbench or are they needed for communication between IP blocks. The following picture is the generated counter example in Platform Designer.

Is there an existing example how to generate an IP block in HLS, implement it in Platform Designer and run it on a FPGA.

Thanks!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

"Are these signals generated just for the testbench or are they needed for communication between IP blocks ", the signals generated to use for connection between IP block. After you have done the system connecttion in platform designer, you can be generated verilog code and run in Quartus. The generated HDL for component can also run in an RTL simulator.

For easily connects components in an Intel FPGA tom simplify system design , the HLS compiler will generate standard interface design for interoperability like avalon-mm, avalon-st and other interface.

All scalar arguments results in an input conduit while all pointer/reference arguments becomes address input.

"Is there an existing example how to generate an IP block in HLS, implement it in Platform Designer and run it on a FPGA", this can be done after use the HLS compiler compile the c code and then implement in platform designer as in chapter 8.2 with link below:

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/hls/ug-hls.pdf

Thanks

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page