- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have a design implemented with system of task in HLS and I want to use it with OpenCL. I wrote the .xml that uses the files in folders: /components and /ip for "REQUIREMENTS" and the "design_internal.v" as the name of the "module". With this, .aoclib was generated and linked to a Opencl code. I am compiling to check the report using:

aoc -rtl -v -l opencl_lib.aoclib exm1.cl

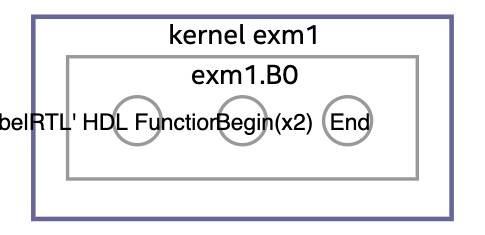

The problem is that I do not see in the system viewer the logic inside the HLS design (even in the folder kernel_hld), it only shows "instruction" elements for inputs (Avalon MM):

When the design is compiled, the amount of resources used is only for dispatch. Do you have some guide about the files from HLS that I have to use to link with OpenCL? Could you give me some advice about this problem?

In case that I have to change the system of task, can I use "ihc::stream" to connect components?

I am using aocl 19.4.0.64 and HLS compiler 19.4.0 with CentOs 7.6

Thanks in advance for advices

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

May I have the design file to compile at my side for further investigation?

Thanks

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page