- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

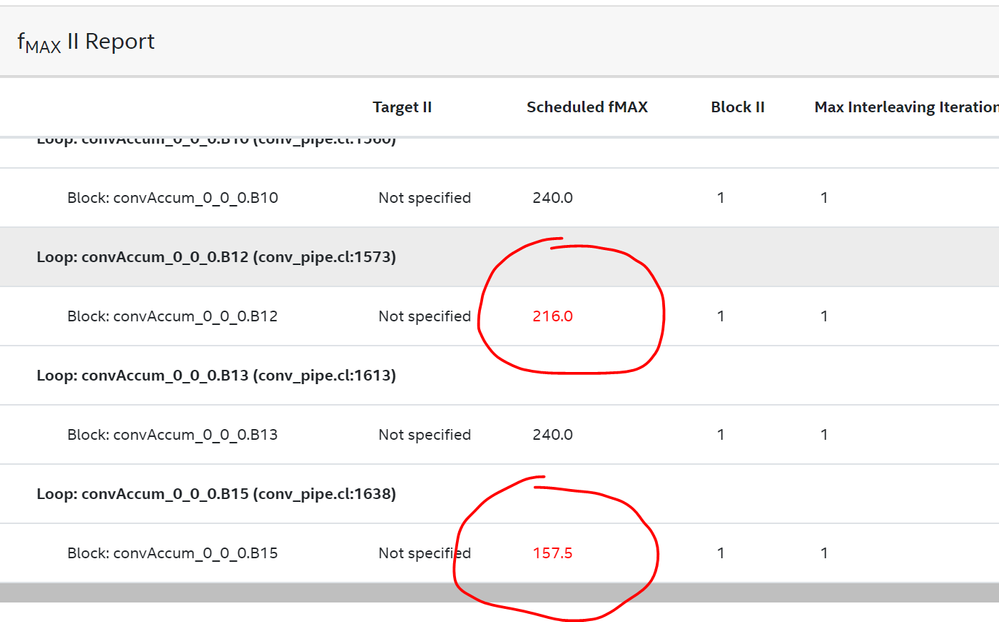

After first stage compilation the report.html shows two low fmax loops as follow:

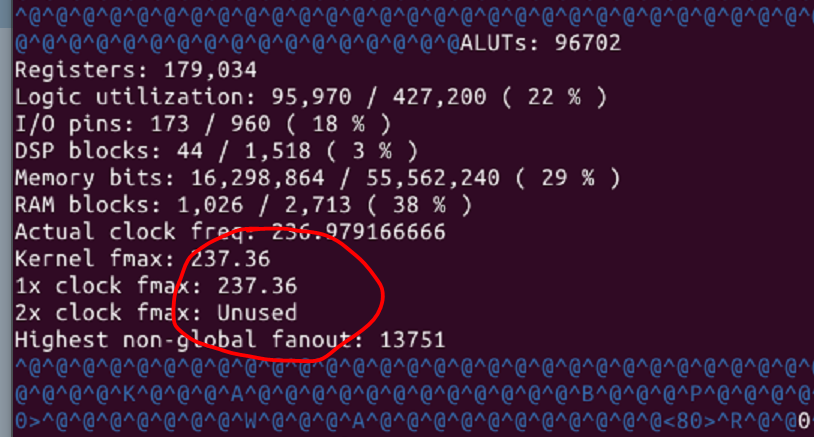

But after P&R, the final fmax achieved is 237Mhz:

How can there be such a big difference between the estimated fmax and the actuallly achieved one ? How should I rely on the early stage report (report.html ) to evaluate the performance of the final design ?

I am using OpenCL SDK v19.1. Thx

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The Fmax values in the HTML are not "estimated" Fmax, they are "target" Fmax. i.e. the OpenCL compiler tries to balance pipeline stages (by inserting extra registers into the pipeline) and use variations of Intel IP Cores towards achieving that Fmax. The target Fmax by default is 240 MHz on Stratix V and Arria 10, and 480 MHz on Stratix 10. The two cases you are getting smaller values in the report are very likely cause by the compiler detecting a design critical path that will likely not meet timing for the target Fmax, and sacrificing Fmax to achieve a loop II one of; if that is the case, there should be a message in the report indicating this. There is no direct relationship between target Fmax in the report and post-place-and-route frequency; you can, however, increase the target Fmax to instruct the compiler to insert additional registers into the pipeline which might give you slightly higher post-place-and-route Fmax, but might also increase loop II if you increase it too far.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page