- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sergey Kostrov wrote:Sergey, thank you for your answer. I've chosen right this method in my project.

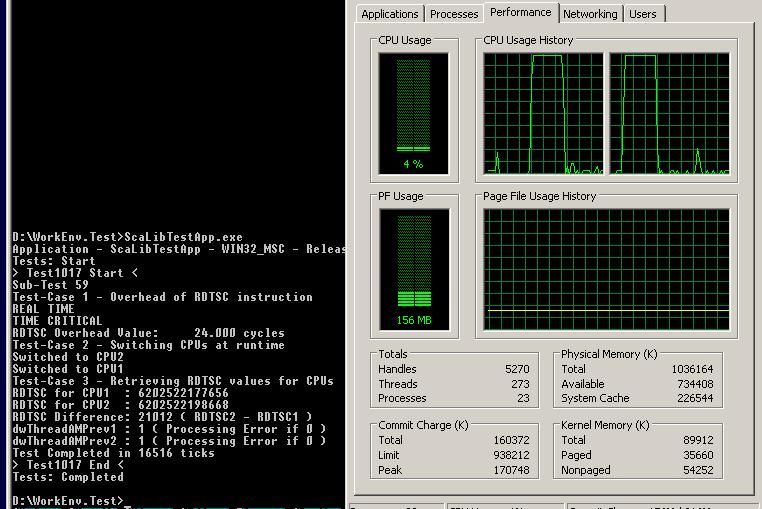

[embed]Hi everybody,

>>[ Roman Oderov ]I have to synchronize time between processors in a multicore system i.e. I have to calculate TSC differences of all

>>processors relative to one of them...

>>...

>>[ Roman Dementiev ] there is no IA instruction that directly returns TSC from the core that you can specify as a parameter...However, if you use a Windows OS there are a couple of Win32 API functions that could help you:

- GetCurrentThread

- SetThreadPriority

- SetThreadAffinityMask

- SleepHere is what I would try:

- [Step00] Let's say you have 2 CPUs ( CPU1 and CPU2 )

- [Step01] Declare a static / global 'Array' of two 64-bit values

- [Step02] Initialize array values with 0

- [Step03] Create a new thread

- [Step04] Set the thread priority to 'Normal'

- [Step05] Set the thread affinity to CPU1 with SetThreadAffinityMask

- [Step06] Call Sleep( 0 )

- [Step07] Set the thread priority to 'Time Critical'

- [Step08] Use inline assembler and call RDTSC and store the value in 'Array[0]'

- [Step09] Set the thread affinity to CPU2 with SetThreadAffinityMask

- [Step10] Call Sleep( 0 )

- [Step11] Use inline assembler and call RDTSC and store the value in 'Array[1]'

- [Step12] Calculate a difference between 'Array[0]' and 'Array[1]'Here are some additional notes:

- an overhead for steps [Step08], [Step09], [Step10] and [Step11] has to be evaluated

- it is very important to call Sleep( 0 ) after a call to SetThreadAffinityMask

- do as many as possible tests and some average differences have to used but they should not exceed some accuracy threshold ( in nano-seconds ) defined in your specsBest regards,

[/embed]

Sergey

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page