- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have being trying to do bus simulation on my avalon slave with avalon mm master bfm.

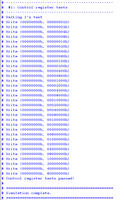

The simulation output is wrong. For example when I write to an address c0 and write data into it, but not writing correctly in the slave. I will share a screenshot below. Do you know why the master not writing into a particular slave address. The second screenshot include a code which I am using to push a command in to the slave.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I saw when slave_0_address is c0, the slave_0_writedata is ff. Do you mean the slave_0_write is not being asserted? Have you checked that there's proper connection between your avalon slave and avalon mm master bfm.

I think the push a command code should be no problem else master bfm wouldn't have proper waveform.

I notice the master bfm waitrequest, have you enable the Assert waitrequest high for master bfm?

Thanks,

Best regards,

Sheng

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I think there is a proper connection between master and the slave. I generated using the qsys. Can we check if it's proper in any other way?

I think I didn't assert waitrequest high but in the waveform, the mo_waitrequest is being asserted towards the end of it right? Is it because not asserting it high?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

In qsys, for the avalon mm master bfm, I had enabled assert wait request high. I had checked it again.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Could you share the qsys top module for taking a look?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am sharing the screenshots below.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sorry, I mean the Qsys top module .v file. Is that possible to provide this for a look? This file will have some interconnections.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Could you provide also the waveform of all signals for master, slave translator and interconnect?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am sharing it below.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Seems like there's no problem with slave translator av_write. The av_write should be connected to slave_0_avalon_slave_0_write and slave_0_avalon_slave_0_write is connected to mm_interconnect_0_slave_0_avalon_slave_0_write. So mm_interconnect_0_slave_0_avalon_slave_0_write by right should be synchronized with av_write. May be you have other initialization in your testbench?

Thanks,

Sheng

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The code snippet in the test bench was shared with you earlier (to push a command). That was the set of statements that I use and I believe there are no other initializations elsewhere.

My doubt is that, when I write c0 to a register, why does the interconnect and the slave avs address show a range of addresses such as from c0 to c4, without specifying them?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I tested those statements without problem. There's no range of addresses being written. Attached two design files for your reference. First design file (avlmm_1x1_verilog.zip) translator result image:

Second design file (qwork.zip) perform single avalon write and single avalon read to pio control then compare the compatible of write and read data image:

Run the run_simulation.tcl. May be can try the testbench inside the files. In testbench, remember to define the correct parameters AV_ADDRESS_W, AV_SYMBOL_W and AV_NUMSYMBOLS.

Thanks,

Best regards,

Sheng

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for the reply and I will look in to those files.

I have an Avalon slave device with an 8-bit data width and multiple individually addressable 8-bit data registers with adjacent addresses. So, sometimes I want to write data to a single 8-bit data register in my address space. The BFM and/or the Avalon infrastructure are generating 4 successive addresses, not the single address I expect. It is as if the BFM and Avalon infrastructure are configured to do a 32-bit write, with 4 successive bytes of data.

First, is it possible to do a single 8-bit write to my slave device?

Secondly, if it is possible, what parameters should I set, and to what values, to achieve this?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Sure. BFM data width will be the multiplication of symbol width and number of symbols. Since the minimum symbol width is 8 so have to adjust number of symbols to 1 in order to get 8-bit data width.

Thanks,

Best Regards,

Sheng

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I had declared it as 8 and 1, but still 4 successive addresses are being written into. What would be causing that if there are no other initializations?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Then, I think you have to use burst write instead of single write already. Or implementing multiple slave IPs to perform single write.

Thanks,

Best regards,

Sheng

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Any further update or concern?

Thanks,

Best Regards,

Sheng

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I tried using your suggestions but the issue still remains. Do you think there's anything further that I could do to address this problem.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Since the BFM push command had been tested before without any problem. Seems like the problem is on the custom slave. I mean before is what will happen if you modify the custom slave device with an 8-bit data width and multiple individually addressable 8-bit data registers with adjacent addresses to custom slave device with an 8-bit data width and single addressable 8-bit data registers?

Thanks,

Best Regards,

Sheng

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Any further update or concern?

Thanks,

Best Regards,

Sheng

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page