- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm trying to mess around with the Cyclone V DSP and have fun triggering different settings that appear in chip planner.

How in the world do I trigger ay_use_scan_in?

Can someone provide a design where ay_use_scan_in is set to true?

What is a scan_in even used for?

Thank you.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Andrue,

Can you provide any snapshot of ay_use_scan_in in chip planner for clearer view?

Thanks,

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

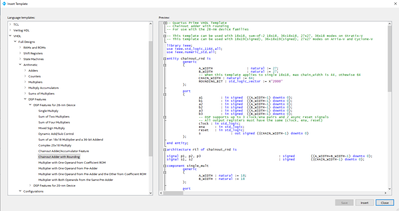

In order to infer the scan-in port for AY, you need to have associated code that points Quartus in the proper direction for synth + place and route. Options include (Quartus 18.1 standard):

- Quartus IP (i.e. via IP Catalog or Qsys/Platform Designer) - Multiplier Adder Intel FPGA IP

- Inference via RTL templates (see screenshot below)

- Using high-level design tool like DSP Builder

Depends on what are you looking to do with that input port. If there isn't an obvious choice from different tabs/selections in the Quartus IP, it should be able to be done by using the various RTL templates in your source VHDL/Verilog.

The templates are meant to infer a base functionality - can be modified for your specific case, but be aware that changes need to align with the functionality found in the user guide (see link below).

I would recommend first using the Quartus IP GUI - this keeps the scope of the changes to the inferred RTL to valid use-cases.

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/cyclone-v/cv_5v2.pdf

Hopefully this helps!

Jeff

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

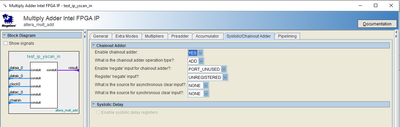

This screenshot is more applicable for using the chain adder. When you select "YES" for chainout adder, then the "chainin" port is activated in the block diagram.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Andrue,

Any updates?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sorry. I've had some issues with my Intel account.

Yeah. I can use the chainadder fine and the chainin port. But, the primitive has a port ay_scan_in, that I can't figure out. I'm not quite sure what it does or how to use it. The only references I see talk about boundary scanning. Is that what the port is used for? Or, is it just left over from the Stratix devices?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page