- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Good afternoon,

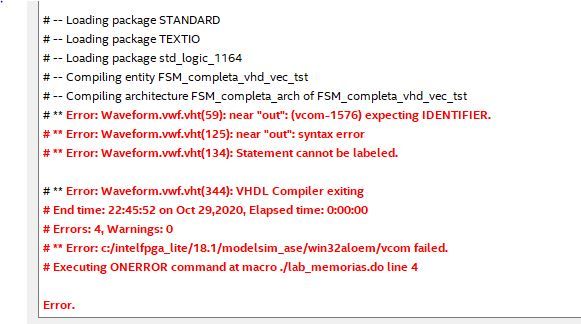

I am designing a finite state machine, I made the datapath with its respective memories and an adder. I also designed a controlpath in vhdl. But when simulating in the Waveform I have an error, apparently it is in the VHDL code.

abjoint image with the simulation error and vhdl code

library ieee;

use ieee.std_logic_1164.all;

entity FSM_LAB4 is

port(

clk : in std_logic;

reset : in std_logic;

load1 : in std_logic;

load2 : in std_logic;

startop:in std_logic;

nextt : in std_logic;

view : in std_logic;

view1 : in std_logic;

view2 : in std_logic;

cnt : in std_logic;

W1 : out std_logic;

W2 : out std_logic;

W3 : out std_logic;

W4 : out std_logic;

W5 : out std_logic;

R1 : out std_logic;

R2 : out std_logic;

rRom1:out std_logic;

rRom2:out std_logic;

wRam: out std_logic;

rRam: out std_logic;

contador : out std_logic;

control: out std_logic

);

end entity;

architecture rtl of FSM_LAB4 is

-- Build an enumerated type for the state machine

type state_type is (s0, s1, s2, s3, s4, s5, s6, s7, s8, s9, s10, s11, s12, s13, s14, s15, s16, s17);

-- Register to hold the current state

signal state : state_type;

begin

process (clk, reset)

begin

if reset = '1' then

state <= s0;

elsif (rising_edge(clk)) then

case state is

when s0=>

if load1 = '1' then

state <= s1;

elsif load2 = '1' then

state <= s3;

elsif view1 = '1' then

state <= s2;

elsif view2 = '1' then

state <= s4;

elsif startop = '1' then

state <= s5;

elsif view = '1' then

state <= s15;

elsif nextt = '1' then

state <= s16;

--else

--state <= s0;

end if;

when s1=>

if view1 = '1' then

state <= s2;

else

state <= s0;

end if;

when s2=>

if load2 = '1' then

state <= s3;

else

state <= s0;

end if;

when s3=>

if view2 = '1' then

state <= s4;

else

state <= s0;

end if;

when s4=>

if startop = '1' then

state <= s5;

else

state <= s0;

end if;

when s5=>

state <= s6;

when s6=>

state <= s7;

when s7=>

state <= s8;

when s8=>

state <= s9;

when s9=>

state <= s10;

when s10=>

state <= s11;

when s11=>

state <= s12;

when s12=>

state <= s13;

when s13=>

state <= s14;

when s14=>

if cnt = '1' then

state <= s0;

else

state <= s5;

end if;

when s15=>

if nextt = '1' then

state <= s16;

else

state <= s0;

end if;

when s16=>

if cnt = '1' then

state <= s17;

else

state <= s0;

end if;

when s17=>

state <=s0;

end case;

end if;

end process;

process (state)

begin

case state is

when s0 =>

W1 <= '0';

W2 <= '0';

W3 <= '0';

W4 <= '0';

W5 <= '0';

R1 <= '0';

R2 <= '0';

wRam <= '0';

rRam <= '0';

rRom1 <= '0';

rRom2 <= '0';

contador <= '0';

control <= '0';

when s1 =>

W1 <= '1';

W2 <= '0';

W3 <= '0';

W4 <= '0';

W5 <= '0';

R1 <= '0';

R2 <= '0';

wRam <= '0';

rRam <= '0';

rRom1 <= '0';

rRom2 <= '0';

contador <= '0';

control <= '0';

when s2 =>

W1 <= '0';

W2 <= '0';

W3 <= '0';

W4 <= '0';

W5 <= '1';

R1 <= '1';

R2 <= '0';

wRam <= '0';

rRam <= '0';

rRom1 <= '0';

rRom2 <= '0';

contador <= '0';

control <= '0';

when s3 =>

W1 <= '0';

W2 <= '1';

W3 <= '0';

W4 <= '0';

W5 <= '0';

R1 <= '0';

R2 <= '0';

wRam <= '0';

rRam <= '0';

rRom1 <= '0';

rRom2 <= '0';

contador <= '0';

control <= '0';

when s4 =>

W1 <= '0';

W2 <= '0';

W3 <= '0';

W4 <= '0';

W5 <= '1';

R1 <= '0';

R2 <= '1';

wRam <= '0';

rRam <= '0';

rRom1 <= '0';

rRom2 <= '0';

contador <= '0';

control <= '0';

when s5 =>

W1 <= '0';

W2 <= '0';

W3 <= '1';

W4 <= '0';

W5 <= '0';

R1 <= '0';

R2 <= '0';

wRam <= '0';

rRam <= '0';

rRom1 <= '1';

rRom2 <= '0';

contador <= '0';

control <= '0';

when s6 =>

W1 <= '0';

W2 <= '0';

W3 <= '0';

W4 <= '1';

W5 <= '0';

R1 <= '0';

R2 <= '0';

wRam <= '0';

rRam <= '0';

rRom1 <= '0';

rRom2 <= '1';

contador <= '0';

control <= '0';

when s7 =>

W1 <= '0';

W2 <= '0';

W3 <= '0';

W4 <= '0';

W5 <= '0';

R1 <= '0';

R2 <= '0';

wRam <= '1';

rRam <= '0';

rRom1 <= '0';

rRom2 <= '0';

contador <= '0';

control <= '0';

when s8 =>

W1 <= '0';

W2 <= '0';

W3 <= '1';

W4 <= '0';

W5 <= '0';

R1 <= '0';

R2 <= '0';

wRam <= '0';

rRam <= '1';

rRom1 <= '0';

rRom2 <= '0';

contador <= '0';

control <= '0';

when s9 =>

W1 <= '0';

W2 <= '0';

W3 <= '0';

W4 <= '1';

W5 <= '0';

R1 <= '1';

R2 <= '0';

wRam <= '0';

rRam <= '0';

rRom1 <= '0';

rRom2 <= '0';

contador <= '0';

control <= '0';

when s10 =>

W1 <= '0';

W2 <= '0';

W3 <= '0';

W4 <= '0';

W5 <= '0';

R1 <= '0';

R2 <= '0';

wRam <= '1';

rRam <= '0';

rRom1 <= '0';

rRom2 <= '0';

contador <= '0';

control <= '0';

when s11 =>

W1 <= '0';

W2 <= '0';

W3 <= '1';

W4 <= '0';

W5 <= '0';

R1 <= '0';

R2 <= '0';

wRam <= '0';

rRam <= '1';

rRom1 <= '0';

rRom2 <= '0';

contador <= '0';

control <= '0';

when s12 =>

W1 <= '0';

W2 <= '0';

W3 <= '0';

W4 <= '1';

W5 <= '0';

R1 <= '0';

R2 <= '1';

wRam <= '0';

rRam <= '0';

rRom1 <= '0';

rRom2 <= '0';

contador <= '0';

control <= '0';

when s13 =>

W1 <= '0';

W2 <= '0';

W3 <= '0';

W4 <= '0';

W5 <= '0';

R1 <= '0';

R2 <= '0';

wRam <= '1';

rRam <= '0';

rRom1 <= '0';

rRom2 <= '0';

contador <= '0';

control <= '0';

when s14 =>

W1 <= '0';

W2 <= '0';

W3 <= '0';

W4 <= '0';

W5 <= '0';

R1 <= '0';

R2 <= '0';

wRam <= '0';

rRam <= '0';

rRom1 <= '0';

rRom2 <= '0';

contador <= '1';

control <= '0';

when s15 =>

W1 <= '0';

W2 <= '0';

W3 <= '0';

W4 <= '0';

W5 <= '1';

R1 <= '0';

R2 <= '0';

wRam <= '0';

rRam <= '1';

rRom1 <= '0';

rRom2 <= '0';

contador <= '0';

control <= '1';

when s16 =>

W1 <= '0';

W2 <= '0';

W3 <= '0';

W4 <= '0';

W5 <= '1';

R1 <= '0';

R2 <= '0';

wRam <= '0';

rRam <= '1';

rRom1 <= '0';

rRom2 <= '0';

contador <= '1';

control <= '0';

when s17 =>

W1 <= '0';

W2 <= '0';

W3 <= '0';

W4 <= '0';

W5 <= '0';

R1 <= '0';

R2 <= '0';

wRam <= '0';

rRam <= '0';

rRom1 <= '0';

rRom2 <= '0';

contador <= '0';

control <= '1';

end case;

end process;

end rtl;

Link Copied

1 Reply

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sorry for idling for some time. Do you able to solve the issue or do you need further help on this?

Reply

Topic Options

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page