- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

I am using Quartus 18.1 with a NIOS processor and uses Eclipse Mars 2.

I have a working system where I have an onchip_mem and an onchip_flash. I can then have some registers in the mem saved to flash when I write a command so they are restored after power cycle.

I am trying to increase the number of registers from 42 to 70. But everytime I change anything in the platform designer regarding the memory map nothing works anymore.

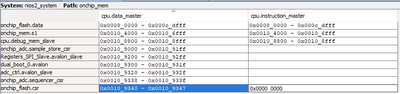

My original memory looks like this:

If I change any of the starting addresses it doesn't work anymore. I also tried to use 'Assign Base Addresses' from the menu.

- After I change the address I generate the HDL.

- Then I go to Eclipse and generates BSP

- Then I compile the Application

- Then I compile Quartus program

- Then I convert programming files and program device

Then nothing gets saved to Flash and I just read 0x00.

Are there anything else I need to do or somehow to easily see what is wrong?

One other observation. If I keep my original code (which is working) and just press 'Assign Base Addresses' then

onchip_adc_sequencer_csr changes address to 0x0010_9330

onchip_flash.csr changes to 0x00109338

And again the flash isn't working anymore.

Any suggestions?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Found the mistake.

The memory initialization file was pointing to a wrong file.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Which settings for the "I am trying to increase the number of registers from 42 to 70." in the Platform Designer did you change?

Can you take a screenshot of that?

Also, if you remain to the original the number of registers of 42 does it work as exepected?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thank you for your reply.

If I just keep the code as it is and keeps the registers at 42 it doesn't work if I use the "Assign Base Addresses".

The code still works, but it doesn't have access to the Flash memory.

I guess it is because onchip_flash.csr changes from 0x00109340 to 0x00109338. I would think that a compile would be enough to make the change and everything work. But that is not the case.

Is there something I am missing?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Your image seems too small, can you share your .qsys file? I can take a look.

May I know what is your intent for your design? Do you just want to access these registers on the OCRAM? And do some read and write?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Found the mistake.

The memory initialization file was pointing to a wrong file.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Oh you mean in the RAM IP settings at the bottom?

Glad you fixed your issue, do you have any further questions?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I’m glad that your question has been addressed, I now transition this thread to community support. If you have a new question, Please login to ‘https://supporttickets.intel.com’, view details of the desire request, and post a feed/response within the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you on your follow-up questions.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page