- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm learning with the ADC-SoC kit. Currently, I'm following the example of ADC_SoC_HIGH_SPEED_ADC using Nios II Eclipse. There are some lines in the code example that I quite don't understand.

In the system header file, the ADC_BASE of channel A is defined as:

#define TERASIC_AD9254_A_BASE 0x61034

In the main file, the register TERASIC_AD9254_A_BASE is written and read by using the functions IOWR and IORD:

int Control = 50000;

IOWR(TERASIC_AD9254_A_BASE, 0x00, Control); //write value to register

Then, print the result as follows:

status_A = IORD(TERASIC_AD9254_A_BASE,0x00); //read value from register

printf("Channel A status = 0x%xh\n",status_A);

At first, I've thought the result would be 0xC350h (as 50000 in decimal equals to C350 in hexadecimal). However, surprisingly the result is 0x1h.

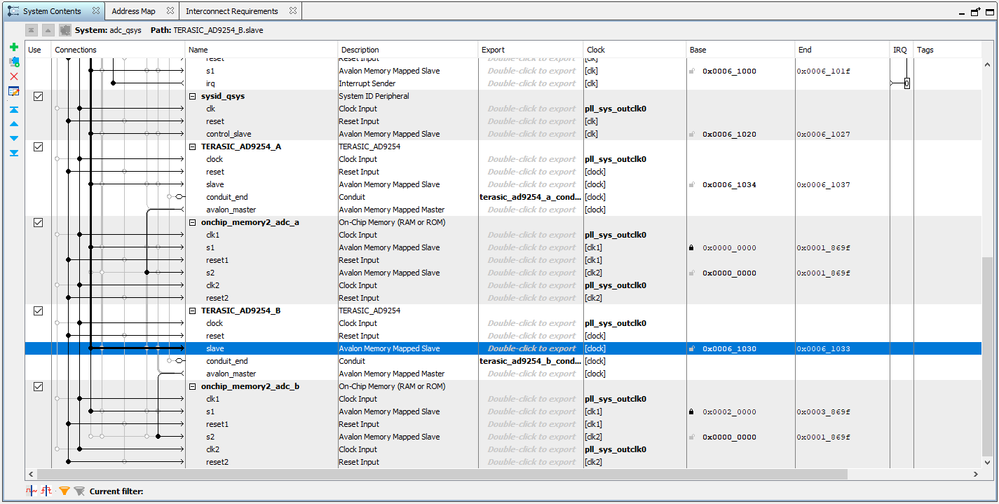

Then, I've opened the Qsys file in the Quartus Prime software and the register is describes as Avalon Memory Mapped Slave.

Can somebody explain me why this configuration leads to the result above ?? Thank you.

Notes: All the code examples can be found from the ADC-SoC system CD, in the directory: \ADC-SoC_v.1.0.5_SystemCD\Demonstrations\FPGA\ADC_SoC_HIGH_SPEED_ADC_HPS_Nios

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Can anybody help me please ??

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

50000 is the sampling rate, not the ADC result. The value is the actual result.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page