- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

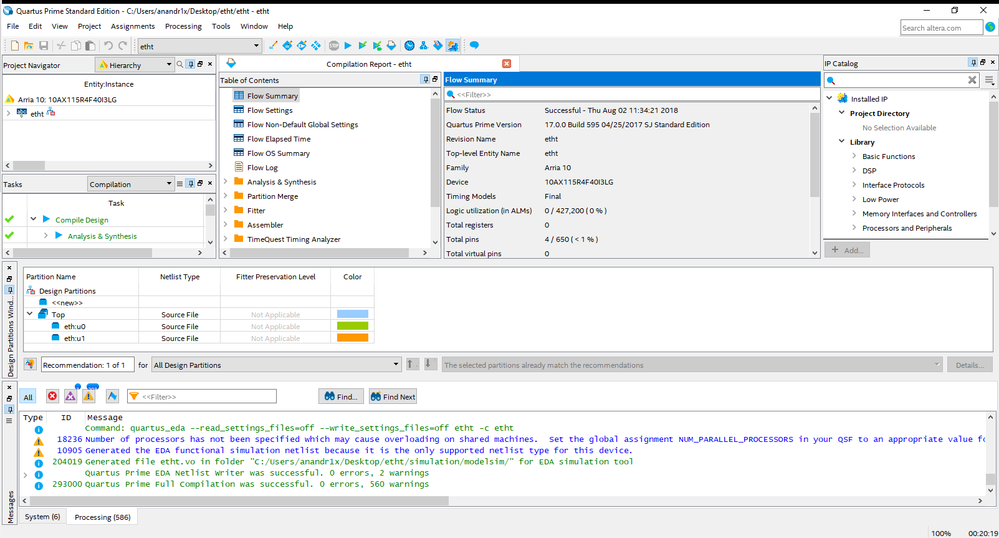

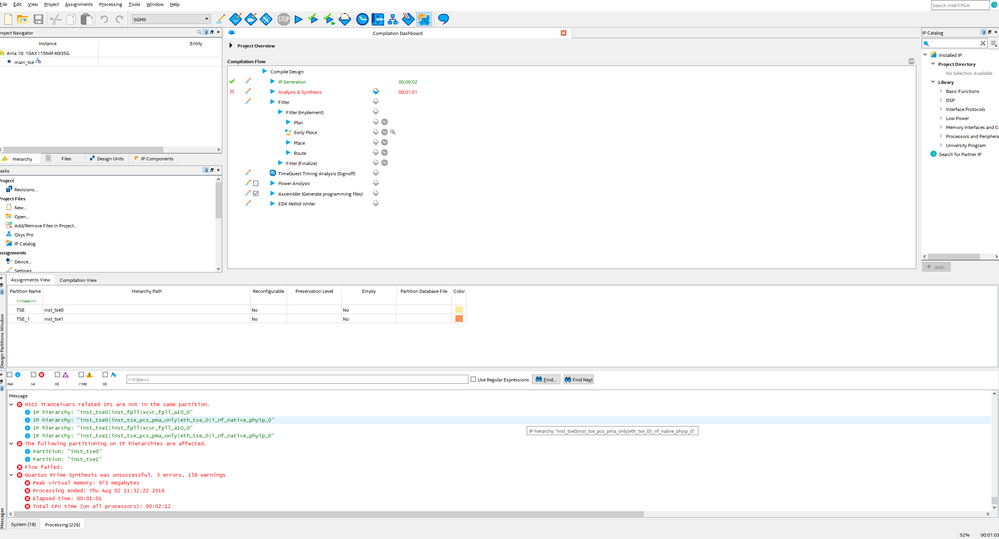

I am making a design that uses Triple Speed Ethernet. My design contains different instances of this IP and I want to define a partition for each TSE instance. However when trying this, Quartus can not synthesise the design and I get this error message

Error(19315): HSSI Tranceivers related IPs are not in the same partition.

Furthermore, TSE instances are independant. So I do not understand why quartus can not make the synthesis of my design. It is worth mentioning that when putting all TSE instances in the same partition, I get no error message. So , is there a way to solve this problem? I am working with quartus 17.0 on the ARRIA 10 FPGA.

Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Apparently, Incremental Compilation can not be done with particular IPs. Actually, hardware IPs like lvds and hps, sould be assigned to the root partition.

Best regards.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

We can successfully compile the TSE instances with independent partition or with merge partition.

Can you share the design file or elaborate more on steps which will help me to recreate the scenario?

Best Regards,

Anand Raj Shankar

(This message was posted on behalf of Intel Corporation)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

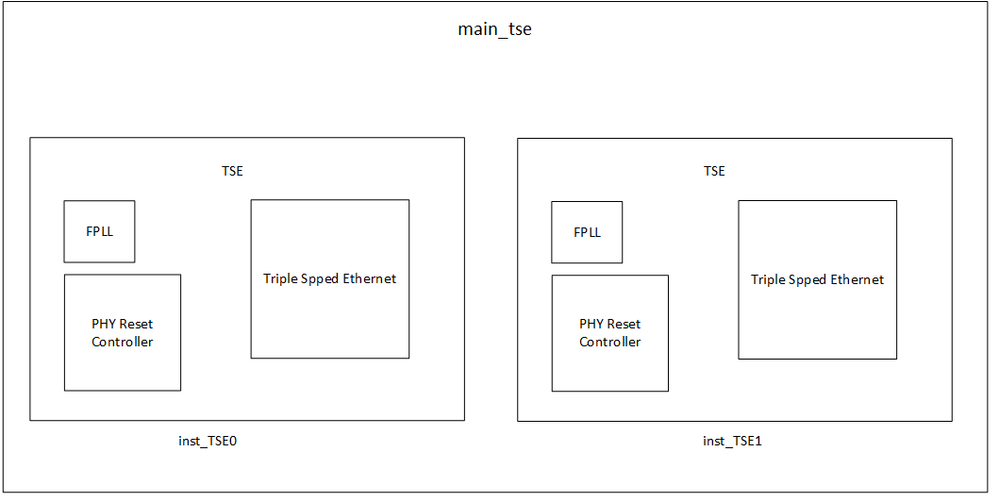

Thank you for answering my question. Actually, I made an entity that contains a Triple Speed Ethernet, an FPLL and a Phy Reset Controller. Then I createde a top level design with two instances of this entity. According to th quartus error messages, I think that the problem is coming from the FPLL and the Phy Reset Controller. I have uploaded the bloc design and the quartue error message.

Best regards.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

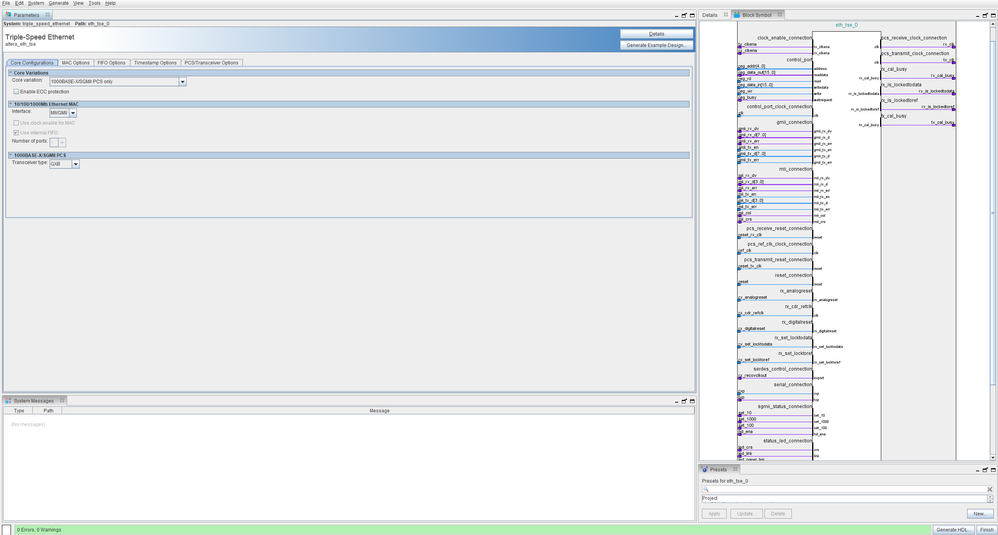

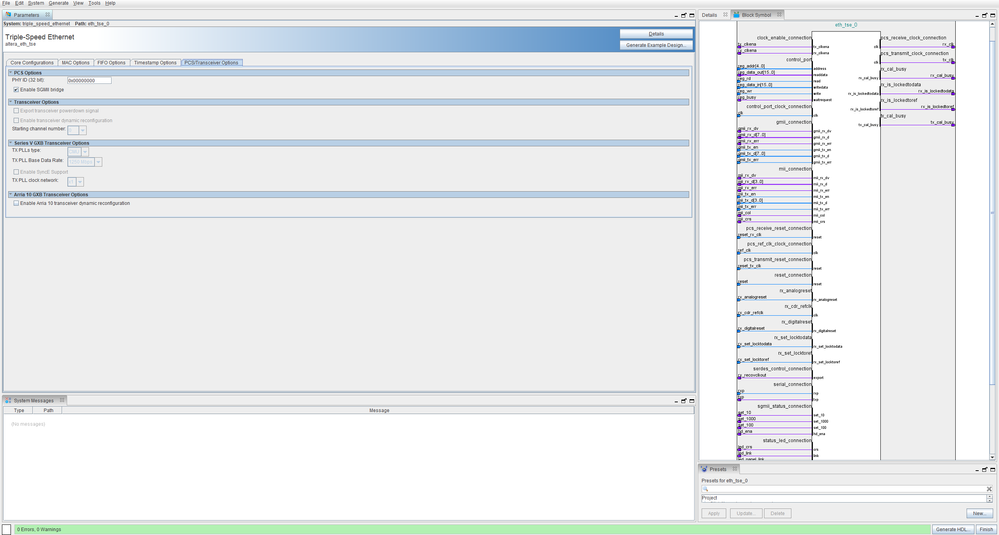

I have forgotten to mention the options that I have chosen for my TSE when creating it with Qsys. The images below indicate my choices. Choosing GXB transceivers implies the use of an FPLL and a phy reset controller.

Best regards.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks,

I have just used setting mentioned in previous posts but not succeeded in reproducing the scenario or error.

Can you share the project file?

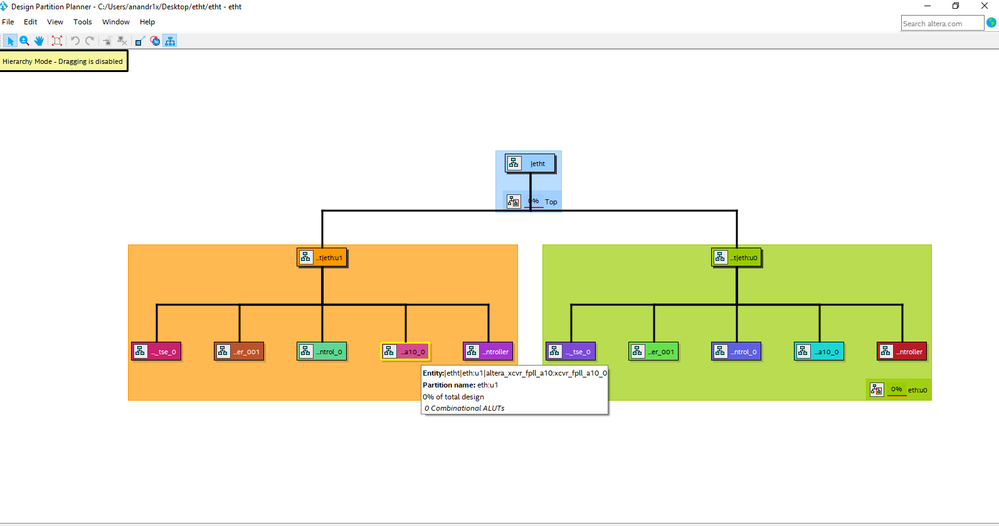

I was able to successfully compile the project attached image for reference.

Best Regards,

Anand Raj Shankar

(This message was posted on behalf of Intel Corporation)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Testing....

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Apparently, Incremental Compilation can not be done with particular IPs. Actually, hardware IPs like lvds and hps, sould be assigned to the root partition.

Best regards.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page