- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Link Copied

2 Replies

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

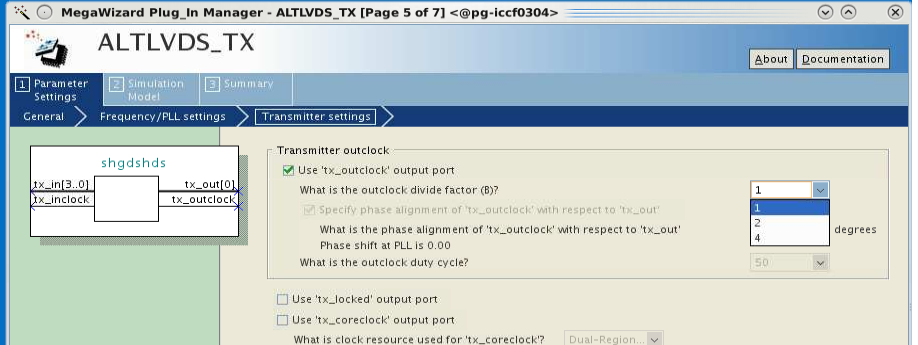

I am not sure which device you are targeting , Here is the screen shot example for Cyclone V. In IP megawizard you can change the core output clock to 1,2 , 4.

Hope helps,

Thank you,

Regards,

Sree

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sree,

Thanks for the reply. I think it is my fault. Everthing in the parameter settings above talks about the input and core clock. Nothing on the output clock. So I assumed te divide ratio was based on the input clock!

I am using Cyclone 10 parts with a serial link of seven bits per. So I need a divide by seven which was one of my options on the screen above.

Now runs fine.

Thanks,

Geoffrey

Reply

Topic Options

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page