- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hai Team,

I'm using Agilex board and trying to interface Axi4Lite IP to HPS via h2f_master port and wrote small application in linux to read from h2f_master port but we are unable to read data from read channel of the AXI4-lite port.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI Manikanta123

In the linux program that you are using how are you reading the memory mapped address?

What address value that you are reading from?

Regards

Jingyang, Teh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hai Jingyang,

We have memory mapped the total address range using mmap function and we are reading from those addresses with the help of below function

unsigned int read_dma(unsigned int *virtual_addr, int offset)

{

return virtual_addr[offset>>2];

}

We are reading from base address of that IP + 0x10 ,when we are reading the value from that address ,it is always show showing zeros.

Regards,

Manikanta

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Manikanta

Could you try to the command "md <address> <value" to read the memory in uboot?

To check if there are value in the memory region consist of value.

- Boot the board.

- Stop the boot flow at uboot.

- Flash the FPGA sof file.

- Enter the command "bdige enable" in uboot.

- Enter the command "md <address> <count>"

Regards

Jingyang,Teh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hai Jingyang,

Thanks for the reply. we tried as you suggested with above steps but the result is same i.e not showing any values in that address .

I checked after linux boot with devmem command also.

Here i attached the steps in u-boot console.

But the same flow is working fine in xilinx board ,i'm able read the data from that address .

Regards,

Manikanta

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Manikanta

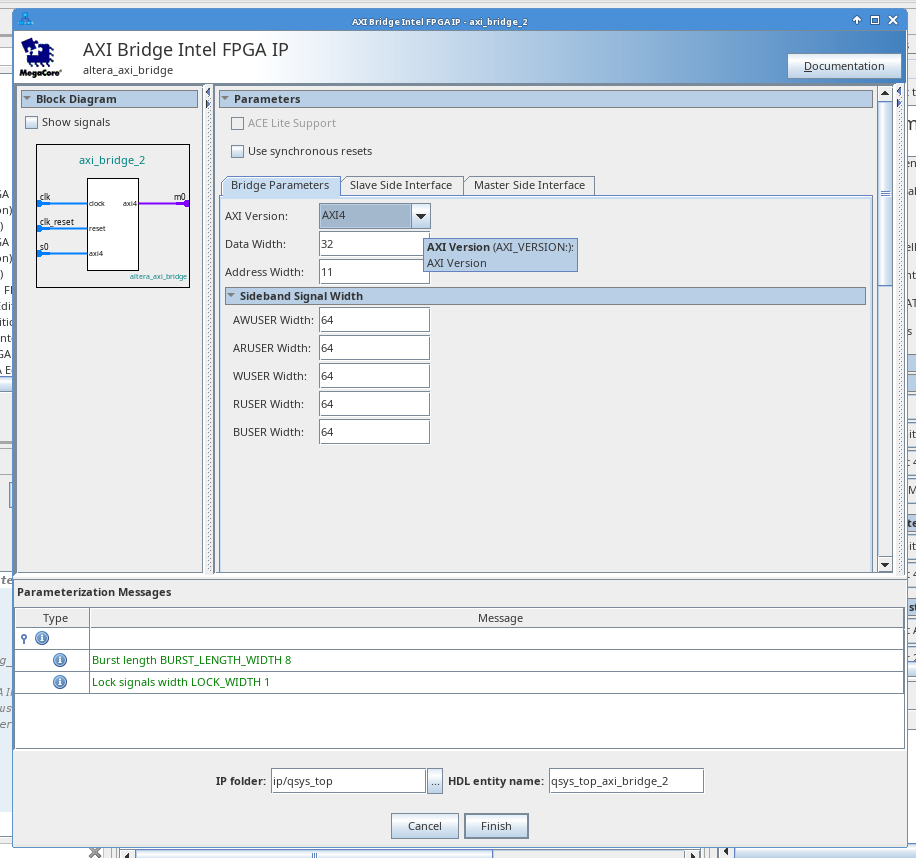

Could you send us a screenshot of the parameters set in regarding the AXI for both HPS and the AXI4lite port?

Regards

Jingyang, Teh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Manikanta

Did you happened to change your qsys design?

I see that the offset address for the IP have changed from 0xd0000 to 0x70000.

Could you try reading the address with offset 0x70000 using the md tool?

If it still cant be read, it seems like you will need to create a custom IP to convert the AXI4 signals to match with AXI4lite.

Unfortunately intel do not have an IP to do the conversion.

However you could try adding an AXI Bridge in between the HPS and the custom IP to see if we could work around this.

With the AXI Bridge there are some additional parameters that you could toggle on/off.

In the master connection, we could turn on the sideband signals to match the HPS and in the slave connection we could do the same to match the custom IP.

You could try toggling between the AXI4 and AXI4lite in the drop down menu as a reference to what signals are required for AXI4lite.

Regards

Jingyang, Teh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

Any update on this forum?

Regards

Jingyang, Teh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hai Jingyang,

We tried as u suggested with Axi bridges in between the IP's but the same issue i.e (rx_gen) is sending always zeros to HPS.

The read channel of rx-gen axi lite ip is always zeros but valid signal are high.

Thanks & Regards,

Manikanta

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Manikanta

Sorry for the wrong information regarding adding an axi bridfe.

The AXI4 master could be connected to the AXI4lite directly and qsys interconnect will connect them together.

Could you try adding a signalTap to capture the signals from AXI4 master and also the AXI4lite slave?

Signals to be look are ACLK,ARADDR,ARVALID,ARREADY,RDATA,RVALID,RREADY & RRESP

Another thing is could you try adding a master jtag and verify the register using systemConsole that the register during run time is having any values?

Regards

Jingyang, Teh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hai Jingyang,

We already check this signals ACLK,ARADDR,ARVALID,ARREADY,RDATA,RVALID,RREADY & RRESP in signal tap but ARADDR,ARVALID,ARREADY signals are high but the data from flowing through RDATA pin is always zero.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Manikanta

Could you try reading the address map using system console?

You could try adding a jtag master in your qsys design and launching the system console from quartus.

What are the value that you are expecting?

Regards

Jingyang, Teh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hai Jingyang,

we have also checked the address map in system console by connecting to the jtag master but the result is always zeros.

we are assigning values to some variables in our custom ip and they are not reflecting back while reading from the HPS.

with regards,

Manikanta

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Manikanta

Do you have a method to read from the custom ip if the values are set?

It is just to rule out any other possibility that what could cause the zero values.

Regards

Jingyang, Teh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Manikanta

Any update on this case?

Regards

Jingyang, Teh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hai Jingyang,

- We have only option to test the incoming data to HPS from Custom IP's of AXI read channel is done through user application or devmem .

- In u-boot, reading the incoming data through md command.

We checked this three methods and in all three methods we are getting zeros.

Note: The Custom IP is generated from Xilinx HLS and we are using those RTL files for Quartus in agilex board.

Other than AXI read data channel all other channels(AW,W,AR) are working fine.

Regards,

Manikanta

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI Manikanta123

I see that the h2f_master port is also connected to another IP.

Is it possible to read from that IP?

Are the values correct reading from that?

Regards

Jingyang, Teh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hai Jingyang,

The h2f_master port is connected to another IP but it is not possible to read from another IP's in FPGA.

Regards,

Manikanta

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Manikanta

Is it possible that HPS reads data from the other IP? just to confirm that the HPS h2f_master is working.

Regards

Jingyang, Teh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Manikanta

Any update on this case?

Regards

Jingyang, Teh

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page