- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am trying to use the unary or operator.

It compiles and simulates fine in ModelSim, but fails to compile in Quartus with the following error message:

Error (10500): VHDL syntax error at file.vhd(#) near text "or"; expecting "(", or an identifier ("or" is a reserved keyword), or unary operator

signal my_flags: boolean_vector(7 downto 0);

if or my_flags then

-- Do something.

end if;

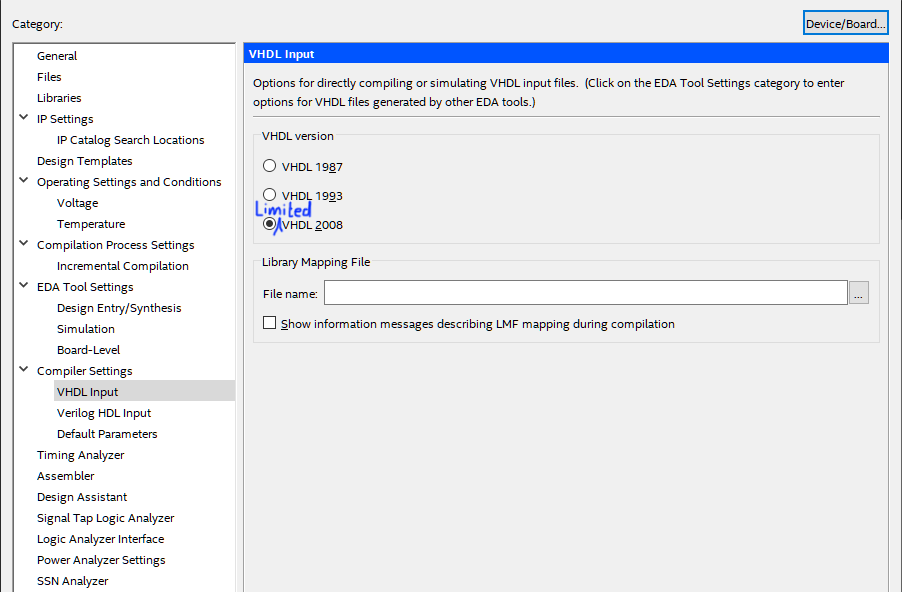

I've ensured that the Settings > Compile Settings > VHDL Input > VHDL 2008 is selected.

Any ideas?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

From Error it is indicating that, there might be issue with syntax of entire VHDL code so It is difficult to support with this piece of code, if possible share entire code here or attach with text/word file.

Regards,

Vicky

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Vicky,

Thanks for responding.

Here is an example that compiles in ModelSim, but not in Quartus.

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity MyFlags is

port

(

clock: in std_logic;

my_flags: in boolean_vector(7 downto 0)

);

end;

architecture V1 of MyFlags is

constant MY_FLAGS_FALSE: boolean_vector(my_flags'range) := (others => false);

begin

process(clock)

begin

if rising_edge(clock) then

-- OK: Compiles in Quartus.

if not(my_flags = MY_FLAGS_FALSE) then

-- Do something.

end if;

-- OK: Compiles in Quartus.

if my_flags /= MY_FLAGS_FALSE then

-- Do something.

end if;

-- OK: Compiles in Quartus.

if my_flags = (my_flags'range => false) then

-- Do something.

end if;

-- Not OK: Won't compile in Quartus, but compiles successfully in ModelSim.

if or my_flags then

-- Do something.

end if;

-- Not OK: Won't compile in Quartus, but compiles successfully in ModelSim.

if or(my_flags) then

-- Do something.

end if;

end if;

end process;

end;Error messages:

Error (10500): VHDL syntax error at test.vhd(38) near text "or"; expecting "(", or an identifier ("or" is a reserved keyword), or unary operator

Error (10500): VHDL syntax error at test.vhd(43) near text "or"; expecting "(", or an identifier ("or" is a reserved keyword), or unary operator

Error (10500): VHDL syntax error at test.vhd(43) near text "then"; expecting ":=", or "<="

It's not obvious to me what the problem is. Could you enlighten me?

Thanks,

Tim.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

'or' is a binary logical operator so please follow the proper syntax.

refer the below attachment about operators from Language resource manual & let me know if you have any different issue.

Regards,

Vicky

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

"or" is three things:

- A unary operator (Page 120 of the file you included). Syntax: or my_vector

- A binary operator. Syntax my_vector1 or my_vector2

- A vectorized overloaded logical operator declared in std_logic_1164 (line 145) and defined in std_logic_1164-body (lines 512-522). Syntax: or(my_vector)

Sources:

- https://standards.ieee.org/standard/1076-2008.html

- https://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=4772740 (Pages 28 and 120)

- https://github.com/ghdl/ghdl/blob/master/libraries/ieee2008/std_logic_1164.vhdl

- https://github.com/ghdl/ghdl/blob/master/libraries/ieee2008/std_logic_1164-body.vhdl

- https://www.doulos.com/knowhow/vhdl_designers_guide/vhdl_2008/

ModelSim has no problem compiling the proper syntax. Are there any other options that I need to select in Quartus to enable proper compilation of IEEE Std 1076-2008? How can I verify whether Quartus is using the up-to-date libraries?

EDIT:

I've written a test package to try to figure out what the problem is.

Quartus successfully compiles the package - both the overloaded unary "or" operator and the function or_test, but it won't compile the if statement that uses the overloaded unary "or" operator.

Could there be a problem with my installation of Quartus?

-- library ieee;

-- use ieee.std_logic_1164.all;

-- use ieee.numeric_std.all;

-- use STD.TEXTIO.all;

package MyTest is

-- OK: Compiles in Quartus.

function "or"(r: boolean_vector) return boolean;

-- OK: Compiles in Quartus.

function or_test(r: boolean_vector) return boolean;

end package MyTest;

package body MyTest is

-- OK: Compiles in Quartus.

function "or"(r: boolean_vector) return boolean is

constant R_FALSE: boolean_vector(r'range) := (others => false);

begin

return r /= R_FALSE;

end function "or";

-- OK: Compiles in Quartus.

function or_test(r: boolean_vector) return boolean is

constant R_FALSE: boolean_vector(r'range) := (others => false);

begin

return r /= R_FALSE;

end function or_test;

end package body MyTest;

library ieee;

library work;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

use work.MyTest.all;

entity MyFlags is

port

(

clock: in std_logic;

my_flags: in boolean_vector(7 downto 0)

);

end;

architecture V1 of MyFlags is

constant MY_FLAGS_FALSE: boolean_vector(my_flags'range) := (others => false);

begin

process(clock)

begin

if rising_edge(clock) then

-- OK: Compiles in Quartus.

if not(my_flags = MY_FLAGS_FALSE) then

-- Do something.

end if;

-- OK: Compiles in Quartus.

if my_flags /= MY_FLAGS_FALSE then

-- Do something.

end if;

-- OK: Compiles in Quartus.

if my_flags /= (my_flags'range => false) then

-- Do something.

end if;

Not OK: Won't compile in Quartus, but compiles successfully in ModelSim.

if or my_flags then

-- Do something.

end if;

Not OK: Won't compile in Quartus, but compiles successfully in ModelSim.

if or(my_flags) then

-- Do something.

end if;

OK: Compiles in Quartus.

if work.MyTest.or_test(my_flags) then

-- Do something.

end if;

-- OK: Compiles in Quartus.

if work.MyTest."or"(my_flags) then

-- Do something.

end if;

-- Not OK: Won't* compile in Quartus, but compiles successfully in ModelSim.

-- * If the MyTest package is commented out, Quartus gives Error (10511): VHDL Qualified Expression error at test.vhd(#): "or" type specified in Qualified Expression must match boolean type that is implied for expression by context

-- * If the MyTest package is compiled, Quartus successfully compiles using work.MyTest."or"()

-- See NOTE 3 on page 28 of IEEE Std 1076-2008

if "or"(my_flags) then

-- Do something.

end if;

end if;

end process;

end;

BTW, a new standard was published recently, IEEE Std 1076-2019: https://standards.ieee.org/standard/1076-2019.html

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for the patience & details.

Are there any other options that I need to select in Quartus to enable proper compilation of IEEE Std 1076-2008?--- -- -- Intel Quartus Pro edition has full support for VHDL-2008, Intel Quartus Standard has limited support, please refer the Page-7 from link below & check your Quartus edition.

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/br/br-quartus-prime-software.pdf

Regards,

Vicky

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

There is no proper compliance available yet & you may find discrepancy in document. In Intel Quartus prime Pro support for VHDL-2008 as follows,

https://www.intel.com/content/www/us/en/programmable/quartushelp/current/index.htm#hdl/vhdl/vhdl_list_2008_vhdl_support.htm

should I consider that case to be close.

Regards,

Vicky

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page