- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

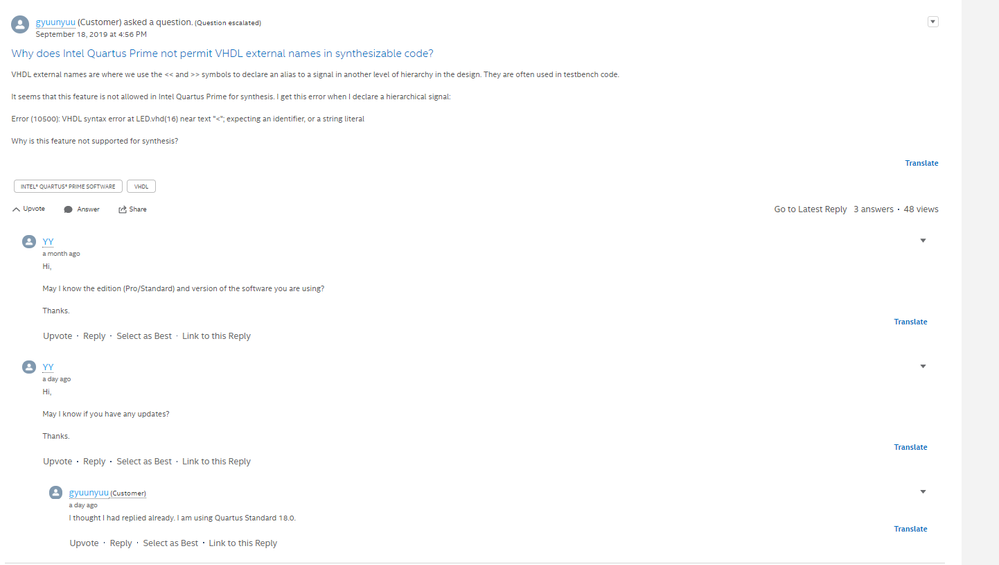

VHDL external names are where we use the << and >> symbols to declare an alias to a signal in another level of hierarchy in the design. They are often used in testbench code.

It seems that this feature is not allowed in Intel Quartus Prime for synthesis. I get this error when I declare a hierarchical signal:

Error (10500): VHDL syntax error at LED.vhd(16) near text "<"; expecting an identifier, or a string literal

Why is this feature not supported for synthesis?

- Tags:

- Vhdl

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

May I know the edition (Pro/Standard) and version of the software you are using?

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

May I know if you have any updates?

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am sorry for missing out the information. I think your reply is not reflected in the forum replies (see below)

Have you tried to compile in the Pro edition? The Standard edition has limited language support for VHDL-2008. You may refer to https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/po/ss-quartus-comparison.pdf.

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I do not have license for the pro edition. It seems that this feature in the language is intended for testbenches and not intended to be supported in synthesis.

This item closes here and no more discussion is required.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Sure. Let me know if you need help.

Thanks.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page