- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

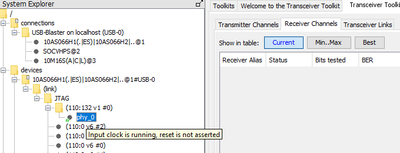

I am using Arria 10 device and Quartus Prime Pro version 17.0. In order to tune and check quality of Transceiver links in my design I am using transceiver toolkit and followed the steps given in the training video. I did connect reconfig_clk and reconfig_reset mentioned in the video but in system console I see transceiver is detected but no information is populated for transceiver channels. I see a message which says "input clock is running, reset is not asserted" but do not what this means.

I have a question about reconfig_reset, is it active high or active low reset and what kind of reset needs to be connected to it? Are there any guidelines about connecting reconfig_clk and reconfig_reset?

I want to use auto sweep feature and have just connected reconfig_clk and reconfig_reset as mentioned in one of the videos.

I referred to below video, let me know if there is any better resource to refer than this video.

http://www.altera.com/customertraining/webex/Transceiver_Toolkit_A10/player.html

Adding screen shot of system console.

Thanks,

Ruturaj.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Chee Pin,

I am also working with Ruturaj on this. We are using a MCP where the Arria 10 is programmed by the CPU. We aren't able to test out the simple design without rewriting all of our IO constraints. Since we are all at Intel, would you be able to meet online? I believe we have a very custom setup.

Thanks,

Justin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

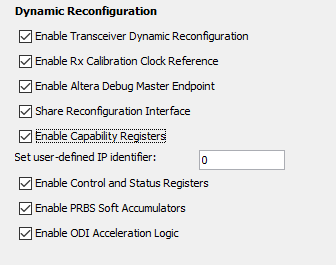

So I'm having exactly the same issue is Quartus Standard 22.1 with the Transceiver Toolkit trying to check the status of transceivers in the JESD204 IP core (configured for recieve only). I've enabled the various parameters necessary to enable the debug master endpoint:

But after compiling and running, no links are shown in transciever toolkit. I just get a blank screen. I can see `phy_0` in the system explorer, which I assume means that the endpoints are correctly set up (I haven't specifically connected thte reconfig interface to a JTAG master as I believe that's what the "Altera Debug Master Endpoint" bit is for). I get the same "input clock is running, reset not asserted" tooltip on the PHY.

I note that this thread is 4 years old. Did you actually find any resolution to this? Could you post any details from your "meeting online"?

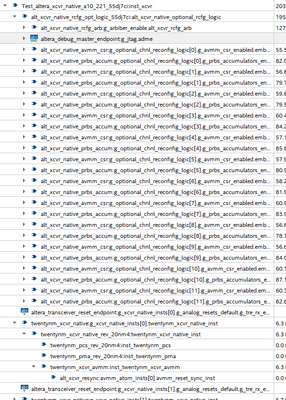

I can't use the example designs because this is not the Arria 10 GX development kit, but rather another SoM product using an Arria 10. But comparing the entity list from the compiled example project, and my project, both seem to have the same contents. The JTAG ADME core is there.

I mean, I'm sure all of you being intel employees is great for you to be able to go offline and have an internal meeting to resolve it, but does absolutely nothing to help your customers who have paid for your products.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

So the only way I could get this working is to manually re-enable all of the ODI Soft Logic parameter code which was commented out and disabled by Altera at some point around Quartus 16

1. Modifying the JESD core TCL files to find any reference to `set_odi_soft_logic_enable` or similar and uncomment them

2. Add the following to a `quartus.ini` file in the project directory:

altera_xcvr_native_a10_enable_odi_acc=on

altera_xcvr_native_a10_debug=on

altera_xcvr_native_a10_advanced=on

altera_xcvr_avmm_a10_advanced=on

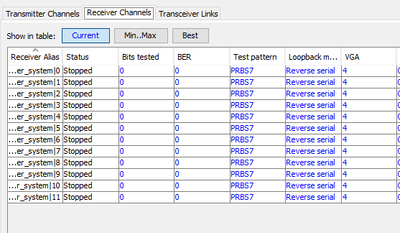

After that regenerate the HDL for Platform Design, recompile, and voila:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello all,

I am having a similar problem.

Trying to debug a JESD IP (receiver only).

I have enabled all the options such as dynamic reconfiguration and connected a JTAG Master.

The System Console does not even recognize any debug endpoint, even though the JTAG Master is recognized in the console.

Any help would be much appreciated.

(we PAID good money for the JESD IP).

Thanks

David

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page