- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello to everyone,

I am using a simple VHDL code in which I have a function defined into architecture's declarative part, but during Analysis and Synthesis, Quartus gives me the following "Quartus Prime software report" :

Problem Details

Error:

Internal Error: Sub-system: CDB_SGATE, File: /quartus/db/cdb_sgate/cdb_sgate_sys.cpp, Line: 3420

iterm != 0

Stack Trace:

0x5bef2: CDB_SGATE_OTERM::insert_fanout + 0x43bd2 (db_cdb_sgate)

0x14bd9: OPT_RAM_POTENTIAL_CANDIDATE::create_true_dual_port_ram_bit_dff + 0x7a9 (SYNTH_INFER)

0xbe1e: OPT_RAM_INFERENCE::create_ram_bits + 0x41e (SYNTH_INFER)

0xa68b: OPT_RAM_INFERENCE::convert_synchronous_ram_sgate_to_nodes + 0xb9b (SYNTH_INFER)

0x9a4b: OPT_RAM_INFERENCE::convert_ram_nodes + 0x4cb (SYNTH_INFER)

0x37278: RTL_SCRIPT::call_ram_rom_fns + 0x220 (SYNTH_OPT)

0x34987: RTL_SCRIPT::call_named_function + 0x597 (SYNTH_OPT)

0x33a08: RTL_SCRIPT::process_script + 0x52c (SYNTH_OPT)

0x33013: opt_process_netlist_scripted + 0x7df (SYNTH_OPT)

0x3a1fa: RTL_ROOT::process_sgate_netlist + 0x1aa (SYNTH_OPT)

0x15d728: SGN_SYNTHESIS::high_level_synthesis + 0x198 (synth_sgn)

0x15e132: SGN_SYNTHESIS::process_current_stage + 0x222 (synth_sgn)

0xc75d5: SGN_EXTRACTOR::synthesize_partition + 0x195 (synth_sgn)

0xc71bf: SGN_EXTRACTOR::synthesis + 0x20f (synth_sgn)

0xc7334: SGN_EXTRACTOR::synthesis_and_post_processing + 0xc4 (synth_sgn)

0x13303: sgn_qic_full + 0x2a3 (synth_sgn)

0x43af: qsyn_execute_sgn + 0x13f (quartus_map)

0x14246: QSYN_FRAMEWORK::execute_core + 0x136 (quartus_map)

0x13d2b: QSYN_FRAMEWORK::execute + 0x49b (quartus_map)

0x1150c: qexe_do_normal + 0x1ec (comp_qexe)

0x16622: qexe_run + 0x432 (comp_qexe)

0x17371: qexe_standard_main + 0xc1 (comp_qexe)

0x1b42b: qsyn_main + 0x53b (quartus_map)

0x13258: msg_main_thread + 0x18 (CCL_MSG)

0x14a5e: msg_thread_wrapper + 0x6e (CCL_MSG)

0x16af0: mem_thread_wrapper + 0x70 (ccl_mem)

0x12af1: msg_exe_main + 0xa1 (CCL_MSG)

0x2a236: __tmainCRTStartup + 0x10e (quartus_map)

0x14033: BaseThreadInitThunk + 0x13 (KERNEL32)

0x73690: RtlUserThreadStart + 0x20 (ntdll)

End-trace

Executable: quartus_map

Comment:

None

System Information

Platform: windows64

OS name: Windows 10

OS version: 10.0

Quartus Prime Information

Address bits: 64

Version: 20.1.1

Build: 720

Edition: Lite Edition

In attechment I have put the archived project.

I did a support service request, but I was adressed here in the Community.

Is there someone that can help me to undertand the reason and how to resolve it?

Thank you in advance.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have duplicate the error and filed a case to the engineering team to check on this.

Will let you know once this is any update.

Best Regards,

Richard Tan

p/s: If any answer from the community or Intel support are helpful, please feel free to give Kudos.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @emaferna

The IE happened in the flow converting inferred RAMs back to logic due to asynchronous read logic and unregistered RAM output.

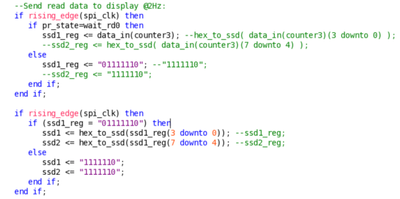

Engineering able to rewrite the design in a way that passes synthesis. Attached the .qar. The main changes can be found in the screenshot below.

The original design defined a true dual port RAM, but the two read ports (corresponding to ssd1_reg and ssd2_reg) are actually reading the same address, so it can be reduced to a simple dual port RAM.

hex_to_ssd and setting of output value to "1111110" are moved to be performed on the registered RAM output rather than the direct RAM output, preserving what is defined in the original design.

Best Regards,

Richard Tan

p/s: If any answer from the community or Intel support are helpful, please feel free to give Kudos.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @emaferna

I have yet to receive any response from you to the previous question/reply/answer that I have provided but I believed that I have answered your question.

With that, I will now transition this thread to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

Best Regards,

Richard Tan

p/s: If any answer from the community or Intel support are helpful, please feel free to give Kudos.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page