- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Cordial greetings, your help has served me well. I have this situation:

I am making an ALU that adds, subtracts, multiplies (3X2 bits), and does logical operations. For this, I use the libraries "IEEE.std_logic_arith.all", "IEEE.std_logic_unsigned.all" and "IEEE.numeric_std.all"; I did the multiplier separately, included it in the project, and "invoked" it.

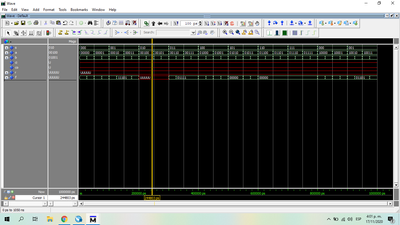

The problem is in the multiplier. The code that I will present to you does compile, however, the RTL simulation (in ModelSim) gives the following answer:

The "UUUUU" output is precisely when s es "010" that is, the multiplier output.

This is the code:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

use ieee.numeric_std.all;

entity alu is

port(

s: in std_logic_vector (2 downto 0);

a: in std_logic_vector (4 downto 0);

b: in std_logic_vector (4 downto 0);

ci: in std_logic;

co: out std_logic;

r: out std_logic_vector (4 downto 0);

f: out std_logic_vector (4 downto 0)

);

end alu;

architecture comportamiento of alu is

component multiplicador

port(

a: in std_logic_vector (2 downto 0);

b: in std_logic_vector (1 downto 0);

ci: in std_logic;

co: out std_logic;

r: out std_logic_vector (4 downto 0)

);

end component;

signal ri: std_logic_vector (4 downto 0);

begin

with s select

f<= a+b when "000",

a-b when "001",

ri when "010",

a or b when "011",

a xor b when "100",

a and b when "101",

"00000" when others;

end comportamiento;

I am very grateful for your help.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Pablovick

First: Your topic is related to VHDL Basics and simulation - not specific for this part of this community!

Please take a closer look to basic documents for VHDL (instances, connecting blocks together, building hierarchical designs ...) and how to control the final performace in silicon at the beginning of every HDL design.

Here a quick-and-dirty-answer:

The signal

ri

is not connected. A function how to build up the "ri" signal is missing also. So, "ri" is always undefined in all cases.

The output of your multiplier is "r" NOT "ri".

The interfacing to generate the final output stage is wrong. You use a simple multiplexer to switch between the two outputs of "alu" and "multpl." which are running in parallel. This is generally not wrong - but you must know HOW TO before doing such things.

Try to rename the output of the multplier from "r" to "ri" and delete the "signal ri ..." line...It should help (if the multplier was tested before and is functional as intended) to give other results before/while/after simulation to you and to step further like try-and-error.

Btw: You run into other problems later because of different bus widths of "a" and "b" and missing registering of in-/outputs.

However, care must be taken to choice the right libraries for the simulation AND target system without produce different - unintended and probably hidden - results.

Good luck,

Regards

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Pablovick

First: Your topic is related to VHDL Basics and simulation - not specific for this part of this community!

Please take a closer look to basic documents for VHDL (instances, connecting blocks together, building hierarchical designs ...) and how to control the final performace in silicon at the beginning of every HDL design.

Here a quick-and-dirty-answer:

The signal

ri

is not connected. A function how to build up the "ri" signal is missing also. So, "ri" is always undefined in all cases.

The output of your multiplier is "r" NOT "ri".

The interfacing to generate the final output stage is wrong. You use a simple multiplexer to switch between the two outputs of "alu" and "multpl." which are running in parallel. This is generally not wrong - but you must know HOW TO before doing such things.

Try to rename the output of the multplier from "r" to "ri" and delete the "signal ri ..." line...It should help (if the multplier was tested before and is functional as intended) to give other results before/while/after simulation to you and to step further like try-and-error.

Btw: You run into other problems later because of different bus widths of "a" and "b" and missing registering of in-/outputs.

However, care must be taken to choice the right libraries for the simulation AND target system without produce different - unintended and probably hidden - results.

Good luck,

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Pablo,

Any update?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Good day, thank you very much for your help.

I have to invoke the multiplier with "por map", create a signal that comunicate the multiplier with "alu" inputs and, at the same time, adapt the 5-bit input to the 3X2 bits of the multiplier.

Thanks a lot

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page