- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Quartus version is 16.1 lite and 18.1 lite.

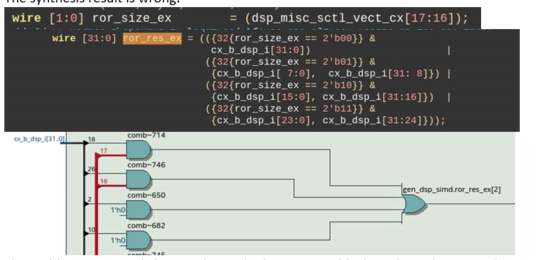

As RTL, ror_size_ex is from dsp_…[17:16], when dsp_...[17:16] is 0, , it should be cx_b_dsp_i

But see the synthesis result, when dsp_...[17:16] is 0, ror_res_ex is always 0.

The synthesis result is wrong. I think it is a quartus bug, do you have some suggestion about this issue if we do not modify RTL.

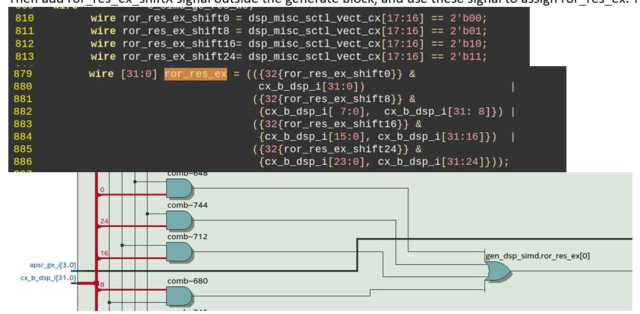

Then add ror_res_ex_shiftX signal outside the generate block, and use these signal to assign ror_res_ex. The synthesis result as below and it seems correct.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Can you post the code or the QAR file for the project. We need the code/project to check it.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi wsive, today I got again similar issue, I am suspecting some issue by file size and or long comment.

They appear and disappear, few hour ago I got deterministic stable behavior, if elsif generate wrong network, case instead generate ok also cleaning project.

After some change to file removing large commented block issue disappeared and never appeared till now using if elsif was stable errantic.....

From error issue to now the version where wrong now compile fine.

I am using VHDl but I observed some similar issues also on verilog and your file has near 1K lines like mine.

Try add a large code commented block (100 lines or more) before and after and see what happen. No more idea for now, I seen other observe intermittent issue.

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

thanks for relay. do you mean, I need try to add a large code commented block (100 lines or more) before the generate block and after the generate block?

the commented block may like below:

/*

-------

-------

-------

...

---------

---------

*/

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi Wsiwe, yes that what I observed, took some code, not garbage, copy paste then comment out. generally I leave between code I rewrote and at end when change apply'd to new code.

I am trying on Linux took 1 minute to build, when I am sure or close to of what trigger this I can try on other platform.

One time I try'd leave compiling on Win7, same behavior, but appear and disappear in a while.

I am also parallel installing last Ubuntu version to avoid comment from Intel clerks and close the loop to culprit of.

Good answer to this was to change vendor, I am too close to deadline.

My Hardware is intended controlling a mechanical with huge moving part and cannot risk the life of none. This is not a game.

Regards

Robert

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

thanks for relay. I try to use synplify_pro to generate .qvm, then use the netlist in quartus. but the route can not pass. when I use RTL, quartus route can pass, but when I use netlist, quartus route can not complete. do you have some suggestion about how quartus fit the netlist generated by synplify? thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Just have a glance at the partial code here, I could not get how would you say that "when dsp_...[17:16] is 0". Is that signal "dsp..." is constant value or a variable?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

it is a variable, in case when dsp..[17:16] is 0. just to show the synthesis result is different from RTL function.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Look at the synthesis result that you think is wrong, the logic for register "ror_size_ex[2]" should be working as this:

1) when dsp_...[17:16] =2 'b0,

cx_b_dsp_i[2] => ror_size_ex[2]

2) when dsp_...[17:16] =2 'b1,

cx_b_dsp_i[10] => ror_size_ex[2]

3) when dsp_...[17:16] =2 'b10,

cx_b_dsp_i[18] => ror_size_ex[2]

4) when dsp_...[17:16] =2 'b11,

cx_b_dsp_i[26] => ror_size_ex[2]

Why it is connected to GND for case 1 & 2, I think that signal "dsp_...[17]" is always high in your coding and make them never happened. Please trace that signal/variable how it is connected. Not sure this would address your question.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page