- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi ,

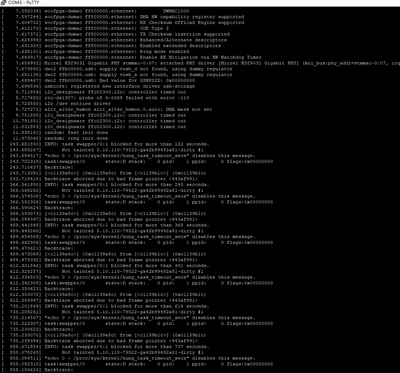

I downloaded Zimage and dtb files to flash, stuck here after booting。and I upload the boot information in boot.txt。Can anyone help me with this problem?

I can't reply to messages, can communicate via email。

U-Boot 2014.10 (Jul 18 2022 - 23:29:51)

CPU : Altera SOCFPGA Arria 10 Platform

BOARD : Altera SOCFPGA Arria 10 Dev Kit

I2C: ready

DRAM: WARNING: Caches not enabled

SF: Read data capture delay calibrated to 1 (0 - 2)

SF: Detected N25Q1024A with page size 256 Bytes, erase size 4 KiB, total 128 MiB

DDRCAL: Success

INFO : Skip relocation as SDRAM is non secure memory

Reserving 2048 Bytes for IRQ stack at: ffe3a6e8

DRAM : 2 GiB

WARNING: Caches not enabled

SF: Read data capture

lay calibrated to 8 (0 - 15)

SF: Detected N25Q1024A with page size 256 Bytes, erase size 4 KiB, total 128 MiB

*** Warning - bad CRC, using default environment

In: serial

Out: serial

Err: serial

Model: SOCFPGA Arria10 Dev Kit

Net: dwmac.ff800000

Hit any key to stop autoboot: 0

FPGA must be in Early Release mode to program core.

fpga - loadable FPGA image support

SF: Read data capture delay calibrated to 1 (0 - 2)

SF: Detected N25Q1024A with page size 256 Bytes, erase size 4 KiB, total 128 MiB

SF: 6225920 bytes @ 0x120000 Read: OK

SF: 32512 bytes @ 0x100000 Read: OK

FPGA BRIDGES: enable

Kernel image @ 0x008000 [ 0x000000 - 0x534158 ]

## Flattened Device Tree blob at 00000100

Booting using the fdt blob at 0x000100

Loading Device Tree to 01ff6000, end 01fff3de ... OK

Starting kernel ...

[ 0.000000] Booting Linux on physical CPU 0x0

[ 0.000000] Linux version 5.10.110-79522-ga42b99492a81-dirty (hh@ubuntu) (arm-none-linux-gnueabihf-gcc (GNU Toolchain for the Arm Architecture 11.2-2022.02 (arm-11.14)) 11.2.1 20220111, GNU ld (GNU Toolchain for the Arm Architecture 11.2-2022.02 (arm-11.14)) 2.37.20220122) #1 SMP Sun Jun 19 23:43:49 PDT 2022

[ 0.000000] CPU: ARMv7 Processor [414fc091] revision 1 (ARMv7), cr=10c5387d

[ 0.000000] CPU: PIPT / VIPT nonaliasing data cache, VIPT aliasing instruction cache

[ 0.000000] OF: fdt: Machine model: Altera SOCFPGA Arria 10

[ 0.000000] Memory policy: Data cache writealloc

[ 0.000000] Zone ranges:

[ 0.000000] Normal [mem 0x0000000000000000-0x000000002fffffff]

[ 0.000000] HighMem [mem 0x0000000030000000-0x000000007fffffff]

[ 0.000000] Movable zone start for each node

[ 0.000000] Early memory node ranges

[ 0.000000] node 0: [mem 0x0000000000000000-0x000000007fffffff]

[ 0.000000] Initmem setup node 0 [mem 0x0000000000000000-0x000000007fffffff]

[ 0.000000] percpu: Embedded 19 pages/cpu s45260 r8192 d24372 u77824

[ 0.000000] Built 1 zonelists, mobility grouping on. Total pages: 522752

[ 0.000000] Kernel command line: console=ttyS0,115200 root=/dev/mtdblock1 rw rootfstype=jffs2

[ 0.000000] Dentry cache hash table entries: 131072 (order: 7, 524288 bytes, linear)

[ 0.00

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi fpga_2022

I tried contacting you through email yesterday with the email address 406313397@qq.com

Could you drop me a mail if the email address is not valid.

My email address is jingyang.teh@intel.com

Regards

Jingyang, Teh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi fpga_2022

Since there are no feedback for this thread or to ,email I shall set this thread to close pending. If you still need further assistance, you are welcome reopen this thread within 20days or open a new thread, someone will be right with you.

If you happened to close this thread you might receive a survey. If you think you would rank your support experience less than 10 out of 10, please allow me to correct it before closing or if the problem can’t be corrected, please let me know the cause so that I may improve your future service experience.

Regards

Jingyang, Teh

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page