- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

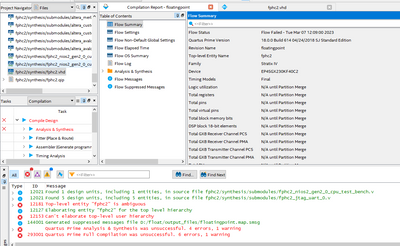

I want to do some calculations which involves floating point with nios ii. So I made qsys system adding floating point hardware 2 component then generated hdl. and add all files to quartus and tried to compile but I got this error.

I search for error and it says repeated file give this error but there is no any file named with my top file. Anyone could you please help me.

Thanks in advance

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Firstly, remove the/all unnecessary files in the "Files" tab in Quartus after you generate HDL in Platform Designer.

Then locate the .qip files in the "synthesis" folder directory that you generated from Platform Designer above.

Add the .qip file in the "Files" tab. And compile your Quartus.

p/s: If any answer from the community or Intel Support are helpful, please feel free to give best answer or rate 4/5 survey.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Can I get the design files from you and let me check from my side ? Also, which Quartus version and OS machine are you working on?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you EBERLAZARE_I_In

Sorry for the delay of my reply.I used windows ,quartus prime standard edition and my device is Stratix iv 230

Here I have attached the project. Please check

Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for the files, I will test it from my side and let you know the results, this might take a few days, I am bit tight up on my side.

Thanks again for your patience.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you very much EBERLAZARE_I_In

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I just got the files downloaded today as we were having issues with our website. I can now check it. I will let you know the update in the next few days.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Firstly, remove the/all unnecessary files in the "Files" tab in Quartus after you generate HDL in Platform Designer.

Then locate the .qip files in the "synthesis" folder directory that you generated from Platform Designer above.

Add the .qip file in the "Files" tab. And compile your Quartus.

p/s: If any answer from the community or Intel Support are helpful, please feel free to give best answer or rate 4/5 survey.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Please check my previous respond, do you have any further update/questions?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Sorry for the delay of my reply and Thank you very much for the reply. It compiled but I did not have top file selected for the project is that okay?

Other thing is when we create the nios II project, what is the project template we should select? .is it float2 functionality, float2 GCC or float2 performance to print our floating point calculation results to the console?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I created project using float2 GCC because it was mentioned that it infer floating point operations provided

by the Floating Point Hardware 2 component.

The try to build project after modifying float_gcc.c file as bellow giving print command

#include <stdio.h>

#include <math.h>

#include "system.h"

#include "float2_gcc.h"

int main(void)

{

int ret = show_gcc_inference();

printf("Result: %d\n", ret);

return ret;

}

but I got error as below

' -msys-lib=hal_bsp -L../ode_bsp/ -L../ode_bsp//newlib/nios2-elf/lib -Wl,-Map=ode.map -O0 -g -Wall -mno-hw-div -mhw-mul -mhw-mulx -mgpopt=global -fno-math-errno -mcustom-fabss=224 -mcustom-fadds=253 -mcustom-fcmpeqs=227 -mcustom-fcmpges=228 -mcustom-fcmpgts=229 -mcustom-fcmples=230 -mcustom-fcmplts=231 -mcustom-fcmpnes=226 -mcustom-fdivs=255 -mcustom-fixsi=249 -mcustom-floatis=250 -mcustom-fmuls=252 -mcustom-fnegs=225 -mcustom-fsubs=254 -o ode.elf obj/default/float2_gcc.o obj/default/float2_gcc_no_custom.o -lm -msys-lib=m

c:/intelfpga/18.0/nios2eds/bin/gnu/h-x86_64-mingw32/bin/../lib/gcc/nios2-elf/5.3.0/../../../../../H-x86_64-mingw32/nios2-elf/bin/ld.exe: ode.elf section `.text' will not fit in region `onchip_memory2_0'

c:/intelfpga/18.0/nios2eds/bin/gnu/h-x86_64-mingw32/bin/../lib/gcc/nios2-elf/5.3.0/../../../../../H-x86_64-mingw32/nios2-elf/bin/ld.exe: address 0x1cff0 of ode.elf section `.rwdata' is not within region `onchip_memory2_0'

c:/intelfpga/18.0/nios2eds/bin/gnu/h-x86_64-mingw32/bin/../lib/gcc/nios2-elf/5.3.0/../../../../../H-x86_64-mingw32/nios2-elf/bin/ld.exe: address 0x1ec4c of ode.elf section `.bss' is not within region `onchip_memory2_0'

c:/intelfpga/18.0/nios2eds/bin/gnu/h-x86_64-mingw32/bin/../lib/gcc/nios2-elf/5.3.0/../../../../../H-x86_64-mingw32/nios2-elf/bin/ld.exe: address 0x1cff0 of ode.elf section `.rwdata' is not within region `onchip_memory2_0'

c:/intelfpga/18.0/nios2eds/bin/gnu/h-x86_64-mingw32/bin/../lib/gcc/nios2-elf/5.3.0/../../../../../H-x86_64-mingw32/nios2-elf/bin/ld.exe: address 0x1ec4c of ode.elf section `.bss' is not within region `onchip_memory2_0'

c:/intelfpga/18.0/nios2eds/bin/gnu/h-x86_64-mingw32/bin/../lib/gcc/nios2-elf/5.3.0/../../../../../H-x86_64-mingw32/nios2-elf/bin/ld.exe: region `onchip_memory2_0' overflowed by 66260 bytes

collect2.exe: error: ld returned 1 exit status

make: *** [ode.elf] Error 1

is this mean my nios 2 onchip memory is not enough? I am using Stratix iv 230 and I set onchip memory as 27000 .

Hope you can give me some advice.

Thank you

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Which Quartus version are you working on is it Lite or Standard? Let me re-check the sizes.

"For the top level of your FPGA-based design might be your Platform Designer system (.qsys). However, the FPGA can include additional design logic."

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thank you very much EBERLAZARE_I_In

Thank you very much for the advices.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for the update, I presume that's it.

Is your board an evaluation board or a custom board? Do you require any further help or any previous help still required?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thank you very much EBERLAZARE_I_In

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Since the compilation issue is solved, I will set the thread to close. You may open a new thread if you have new questions.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I’m glad that your question has been addressed, I now transition this thread to community support. If you have a new question, Please login to ‘https://supporttickets.intel.com’, view details of the desire request, and post a feed/response within the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you on your follow-up questions.

p/s: If any answer from the community or Intel Support are helpful, please feel free to give best answer or rate 4/5 survey.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page