- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I'm now using the interval timer ip on HPS, I set the ip as general purposed timer.

The timer is set to 100 ms and there is a timer_palus link to my fpga led[1]

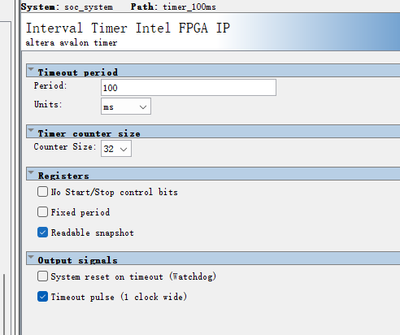

The setting is as shown:

And it was linked to fpga only AXI bridge and Avalon mm bridge.

I called the timer as shown using C:

Then I charged the timer by following orders:

*(Timer+1) = 0b1010 //Stop-1 Start-0 count -1 ITO-0

*(TImer+2) = 0x10& 0xFFFF;

*(Timer+3) = (0x10>>16)& 0xFFFF;

*(Timer+ 1) = 0b0110; //Stop-0 Start -1 count -1 ITO - 0

That should start the timer.

And I set a while loop to wait for the LED[1] to bilink for it is linked to the timeout export.

But nothing happend.

And when I want to read the *(Timer) status the TO bit is always 1 even if I set it to 0.

So my questions are:

1. What happened? Why the timer status of TO is always 1?

2.Why the led[1] didn't blink?

3. What should I do to fix it?

4. By setting the period register, ex. = 10, is that mean the timer was set to 10*100 ms?In another word, if the timer is fixed period, is that mean timer is set to 100 ms?

In case my top level file is wrong I attached my top level file, there is only one line related to the timer:

assign LEDR[1]=timer_export or something.

reguards.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi CAlex

Have you tried teh simulation? Is the design working in simulation?

Could you share me your quartus project? So I could try the design on my end.

Regards

Jingyang, Teh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I haven't yet.

Could you tell me which simulation tool is available on quartus prime lite?

Also I attached my quartus project.

Thank you for your willing to help.

reguards.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It seems I can't reset the TO bit, when I wish to reset the bit it turns to 1 immediately.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

What I trying to get is a flag signal stays high for one clock wide and flip down for one clock wide and so on.

while (1)

{

if (*timer == 3)

{

*timer = 0;

!flag;

}

*led = flag;

};

It didn't work ,the flag stays the same when I read that.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Alex

Could you give me more time to look into this?

I will get back to you as soon as possible this week.

Regards

Jingyang, Teh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Sure, please take your time.

Another thing I want to mention is that I'm using Linux system not the baremetal system, so any related HWlib is not useful.

Yet still I think the problem is on the FPGA side.

Thank you for your kindly willing to help

Wish you have a nice day.

reguards.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

I am having a hard time to generate the simulation.

This week i will try out the design on the DE10 board.

Sorry for the slow progress.

Regards

Jingyang, Teh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Noted, please take your time.

Have a nice day.

reguards.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sure thing,

Please take your time.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Alex

I managed to get the design running in simulation as I got a problem getting hands on to a devkit.

The design is not running is because of the reset.

The FPGA reset is coming from the "Clock Source IP" and it should not be force to always reset.

Please find the attached timer.v

Regards

Jingyang, Teh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Alex

Did you managed to get the design working?

Are you facing any problem so far?

Regards

Jingyang, Teh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Sorry I didn't get that,

Please let me ask the question in another way:

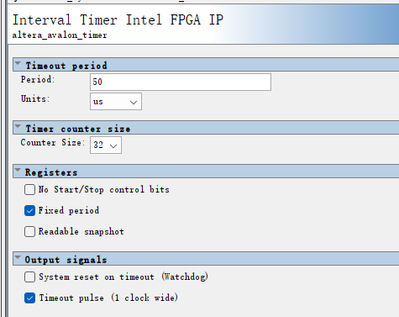

In FPGA soft IP core there is a timer_pulse choise:

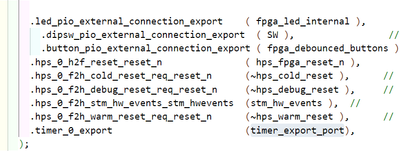

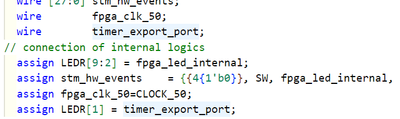

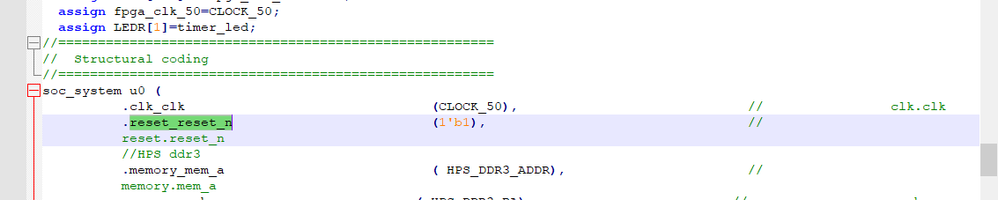

So I enabled this option and in top level verilog I linked that timeou_pulse to my LED[1] as shown:

top level u0

assignment

I started the timer in my user space code by writing 0110 on my control register:

userspace code

And observed the LED[1], it didn't blink on my board.

Please forgive me if my previouse posted questions confused you.

I attached the updated project for you.

You may need to change some LED pins if you are willing to run on Altera De10 standard.

My board is Terasic De10 standard.

Thank you for your willing to help.

Sorry for inconvenience.

Reguards

Alex

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Alex

From your project top-level design. (Timer.v)

You have force the reset pin of the "Clock Source IP"

The "Clock Source IP" controls all the reset line of the other IP including the "Interval Timer IP"

By forcing the "Clock Source IP" in reset, it is putting the "Interval Timer IP" in reset.

Regards

Jingyang, Teh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Alex

Any update on this case?

Regards

Jingyang, Teh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

Since there are no feedback for this thread, I shall set this thread to close pending. Please login to ‘https://supporttickets.intel.com’, view details of the desire request, and post a feed/response within the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you on your follow-up questions.

If you happened to close this thread you might receive a survey. If you think you would rank your support experience less than 10 out of 10, please allow me to correct it before closing or if the problem can’t be corrected, please let me know the cause so that I may improve your future service experience.

Regards

Jingyang, Teh

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page