- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello, hope everyone is doing fine.

I am facing a problem with a digital image processing project that I am currently implementing on the DE1SOC FPGA.

My proposed architecture is a generation of ROWS x COLS of a 1-bit input/output cell which will perform the digital image processing on the input image (the cells are connected together in hardware). (My hardware involves shift registers and other components).

So i am trying to make an interface between the FPGA and the HPS (ARM-9).

My plan is, for example if i have a 5x5 image in C, i want to send 1 bit of each element/pixel from the HPS to the fpga every single cycle ( of course we need handshaking between the fpga and the hps in that case), and then after a number of cycles i want to also receive the data bit by bit and store them into an array as integers.

The de1soc has an heavyweight AXI-bus which can send 128bits at once.

so i was thinking if its possible to send 128 bits to my design ( which each bit of the 128 is actually 1 bit of an 8bit pixel, so in other words ill be sending 1 bit from each of the 128 pixels (8times), and then receive them the same way 1 bit at a time and store them in a new array).

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

If you're trying to use only 1 bit out of the 128 bit of the AXI bridge, it's not really practical.

Can you take a look at this example see if this is similar on what you're trying to achieve?:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello, thanks for the reply!

I think, my explanation in the thread was not really clear. Sorry, I don't have that huge experience with FPGA's so I am going to explain what I want to do using some sketches I made.

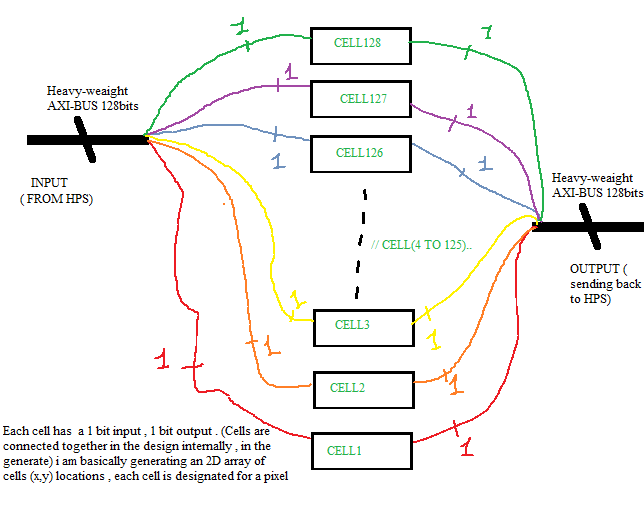

Okay so in the following sketch as you can see;

I want to use the full power of the heavy-weight* AXI-BUS (128bits). Basically ill be sending 128 bits to my design, but each bit of the 128 is going to be sent to a cell of the 128 cells.

The cell I made is serial so it has 1-bit I/O's (includes shift registers and other extc).

ill be sending to each cell a pixel (8-bits), so i will be repeating the process i made below 8 times. in order to fill the reg in the cell.

ill be doing it as the following: 1 bit at once to assure speed and efficiency.

Now technically, that was the easy part. the harder part now is the following :

that's the hard part, doing the thing from the HPS side. this must be done as shown for inputting the image and also when i want to receive the image.

Thanks in advance!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Unfortunately, we don't have the example designs and driver for using the HPS for image processing.

You could take a look at our VIP UG on which IP would suite your desire and see if the example design on DVI Display below would help:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Do you have any further questions?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

As we do not receive any response from you on the previous question/reply/answer that we have provided. Please login to ‘https://supporttickets.intel.com’, view details of the desire request, and post a feed/response within the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you on your follow-up questions.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page