- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I am having issues making my C file with the EDS editor. I am using 18.1 . My goal is to compile my C code with the below make file. However, whenever I attempt to run the make file, I get the following error:

$ make

C:/intelFPGA/18.1/embedded/ip/altera/hps/altera_hps/hwlib/include/hwlib.h:56:2: error: #error You must define soc_cv_av or soc_a10 before compiling with HwLibs

#error You must define soc_cv_av or soc_a10 before compiling with HwLibs

I have read some forum posts which suggest to include this in the make file:

ALT_DEVICE_FAMILY = soc_cv_av

however, this has not helped me.

Any suggestions?

Here is my make file:

#

TARGET = my_first_hps-fpga

CROSS_COMPILE = arm-linux-gnueabihf-

CFLAGS = -static -g -Wall -I${SOCEDS_DEST_ROOT}/ip/altera/hps/altera_hps/hwlib/include

LDFLAGS = -g -Wall

CC = $(CROSS_COMPILE)gcc

ARCH= arm

build: $(TARGET)

$(TARGET): main.o

$(CC) $(LDFLAGS) $^ -o $@

%.o : %.c

$(CC) $(CFLAGS) -c $< -o $@

.PHONY: clean

clean:

rm -f $(TARGET) *.a *.o *~

and here is the top portion of my c file:

#include <stdio.h>

#include <unistd.h>

#include <fcntl.h>

#include <sys/mman.h>

#include "hwlib.h"

#include "socal/socal.h"

#include "socal/hps.h"

#include "socal/alt_gpio.h"

#include "hps_0.h"

Thank you,

James

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Have you checked out the example projects included with your Demo Board? It may be a simple syntax error.

According to the documentation, the makefile should contain:

#

TARGET = my_first_hps-fpga

#

ALT_DEVICE_FAMILY ?= soc_cv_av

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thank you for your reply.

I was suspicious of a typo myself at first. Fortunately my demo board (de0 nano SOC) provides a make file and main.c file which I have been using so I don't think that I have any typos.

I'm wondering if it has something to do with the version of EDS that I am using. I think the de0 nano board came out on version 13.1 so I might try downloading that to see if it helps any. But I feel like there must be a way to make it work for EDS version 18.1 (and later). Do you have any other suggestions?

Thank you,

James

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ,

Can you please try to use the sample make file given in the answer in the below forum post, change it as per your needs and let us know the results.

https://forum.rocketboards.org/t/soc-cv-av-or-soc-a10-before-compiling-with-hwlibs/1956/2

Thanks and Regards

Anil

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Thank you for your reply AnilA.

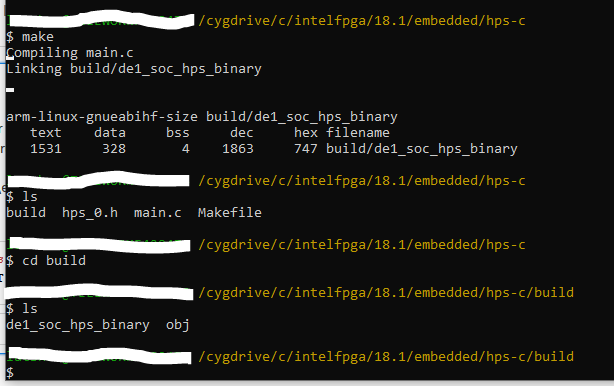

So I did see that forum post in the past and when I tried it, it did not work for me. However, this time whenever I tried it, I moved my make file and main.c file into the directory structure of my 18.1 EDS and now it seems to work. I still need to load the executable into the fpga to verify results. Does this seem reasonable to you? I would think that I should be able to run makefiles in any folder that I can navigate EDS into. What are your thoughts?

C:\intelFPGA\18.1\embedded\ is where the Embedded_Command_Shell.bat

C:\intelFPGA\18.1\embedded\hps-c is where my make file and main.c fileare

see the below screen shot:

copy of my make file (for whoever it may help):

Best Regards,

James

# This is the name of the binaries that will be generated

TARGET = de1_soc_hps_binary

# The device family (soc_cv_av = Cyclone V ; soc_a10 = Aria 10)

ALT_DEVICE_FAMILY = soc_cv_av

# Some paths (Default should work)

HWLIBS_ROOT = ${SOCEDS_DEST_ROOT}/ip/altera/hps/altera_hps/hwlib

# Here we add all *.c files that we want to compile

CSRCS = main.c

# Here we add all *.cpp files that we want to compile

CPPSRCS =

# Here we add the paths to all include directories

INCS =

# Parameters for SCP upload. Set up SSH keys to bypass password prompt

SCP_TARGET_IP = 192.168.1.100

SCP_USER = root

SCP_TARGET_PATH = /home/root

SCP = SCP

SCP_FLAGS =

# Compiler settings

ARCH = arm-linux-gnueabihf

LD = $(ARCH)-g++

CC = $(ARCH)-gcc

CPPC = $(ARCH)-g++

SIZE = $(ARCH)-size

CFLAGS = -g -std=gnu99 -Wall

CPPFLAGS = -g -std=c++11 -Wall

LDFLAGS = -g -Wall

################################################################################

# Don't change anything below this line #

################################################################################

# Some directory and file magic

BUILDDIR = build

OBJDIR = $(BUILDDIR)/obj

# Generate the object names

OBJS = $(addprefix $(OBJDIR)/,$(addsuffix .o,$(basename $(CSRCS:%.c=%.o))))

OBJS += $(addprefix $(OBJDIR)/,$(addsuffix .o,$(basename $(CPPSRCS:%.cpp=%.o))))

# Add some paths

CFLAGS += $(INCS:%=-I%) -I$(HWLIBS_ROOT)/include -I$(HWLIBS_ROOT)/include/$(ALT_DEVICE_FAMILY) -D$(ALT_DEVICE_FAMILY)

CPPFLAGS += $(INCS:%=-I%) -I$(HWLIBS_ROOT)/include -I$(HWLIBS_ROOT)/include/$(ALT_DEVICE_FAMILY) -D$(ALT_DEVICE_FAMILY)

LDFLAGS += $(INCS:%=-I%)

# This is the default target if the user does just calls 'make'

all: build size

# Build all the files

build: builddirs $(BUILDDIR)/$(TARGET)

# Create the required directories (if not already existing)

builddirs:

@mkdir -p $(BUILDDIR)

@mkdir -p $(OBJDIR)

# Link everything together

$(BUILDDIR)/$(TARGET): $(OBJS)

@echo Linking $@

@$(LD) $(LDFLAGS) -o $(BUILDDIR)/$(TARGET) $(OBJS)

# Compile c files

$(OBJDIR)/%.o: %.c

@mkdir -p $(dir $@)

@echo Compiling $^

@$(CC) $(CFLAGS) -c -o $@ $^

# Compile cpp files

$(OBJDIR)/%.o: %.cpp

@mkdir -p $(dir $@)

@echo Compiling $^

@$(CPPC) $(CPPFLAGS) -c -o $@ $^

# Print size information

size: $(BUILDDIR)/$(TARGET)

@echo

@echo

$(SIZE) $^

# Clean up

clean:

@rm -rf $(BUILDDIR) $(OBJS) $(TARGET) $(TARGET).* *.a *.o *~

@echo Done

# Clean must be a phony target so make knows this never exists as a file

.PHONY: clean

# Upload to target

upload:

$(SCP) $(SCP_FLAGS) $(BUILDDIR)/$(TARGET) $(SCP_USER)@$(SCP_TARGET_IP):$(SCP_TARGET_PATH)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you so much James, this worked for me. I was close to failing this project in school. You are a gem!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Just a follow up, I was able to load the binary onto the de0 soc board and control the FPGA LEDS from the HPS (so cool!).

I have no idea whey the EDS is so picky, but maybe this is just one of those 'tips and tircks' to keep in mind.

Thanks,

James

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ,

Glad to know that the issue is resolved.

Thanks and Regards

Anil

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page