- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello.

I trying to transfer data between two Arria VGZ with Custom PHY.

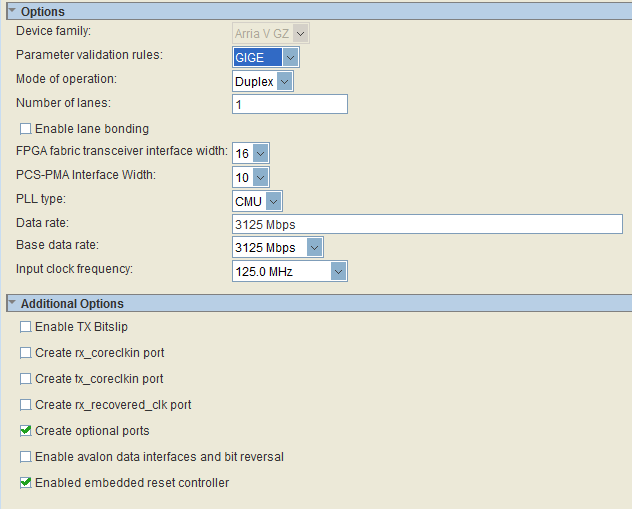

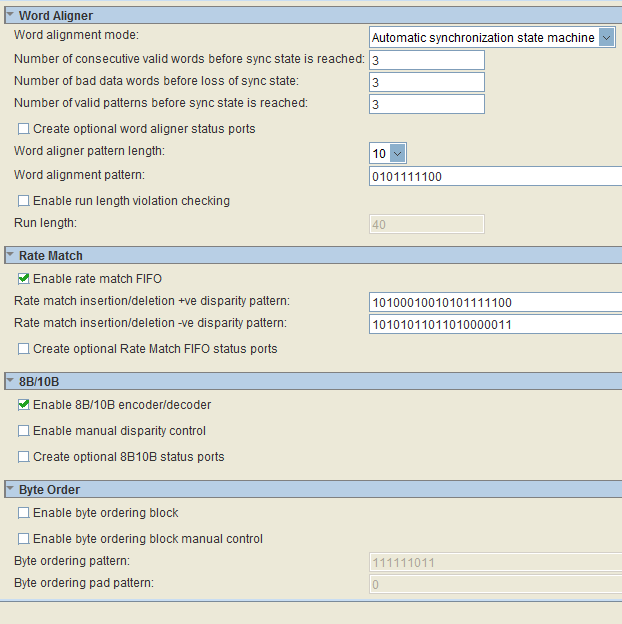

I use 2.5 Gbps preset, i.e. Standard PCS on gige mode with word aligner and rate match fifo (settings attached).

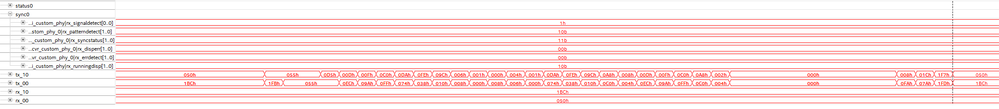

Between packages I pass the IDLE special code group - {9'h050,9'h1BC}. At the beginning of the package - 9'h1FB. At the end of the package - 9'h1FD.

Depending on the length of the package I add Carrier_Extend - 9'h1F7 or 9'h1F7,9'h1F7.

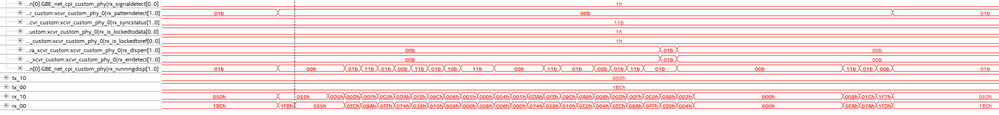

rx_syncstatus undicates that the synchronization is acquired. But as a result, there are disparity errors at the reception (Attached a signal to transmit and receive).

Project has no slack in TimeQuest.

Maybe I missed something when setting up Custom PHY or forming a frame?

Thank you for any help.

- Tags:

- Arria® V FPGAs

Link Copied

0 Replies

Reply

Topic Options

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page