- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, everyone,

It really confused me now. I want to creat a Avalon-ST streaming source component for my ADC in Qsys. The ADC data will be read by NIOS II CPU with SG-DMA. Now, in my component, the Avalon signals are: ready, valid, data, clock, reset. And there are two conduits: ADC_OE, ADC_data. But I don't known how to control the ready signal, since I found the ADC_OE, which is actived by the ready signal, is de-asserted some time. Any advice please.Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Now I realize that the ready signal is automaticlly assertted by Avalon-ST streaming sink(SG-DMA). And how about the valid signal ? Is it necessary for me to assert the valid signal in my component ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

For an ADC, you probably want to ignore the "ready" signal from the sink and either ommit the "valid" signal or leave it stuck at '1' in your source component.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The ready signal is controlled by sink and You must control valid pin with Your source. Valid pin must be asserted only when valid data is sent through the interface... The SGDMA will deassert ready signal if it's input FIFO will be full.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Is it necessary to define a FIFO in my ADC component ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

No it's not necessary but I highly recommend having one. When you are sampling from the ADC you don't want to run into cases where the SGDMA back-pressuring causes you to loose samples. With a FIFO you can help prevent these cases since the FIFO will fill up as apposed to samples being lost. The easiest way is to use the DCFIFO megafunction which you clock at the same rate as the ADC on the input side and use the SGDMA clock frequency on the output side of the FIFO. You drive the output into the SGDMA as a Avalon-ST source interface with the valid signal connected to 'FIFO not empty' and drive the FIFO read acknowledge with 'FIFO not empty & source ready'.

You can use the dual clock FIFO component in Qsys to do this and just export the input side out of the system and hardcode the valid signal into it to constantly write samples into it as well.- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

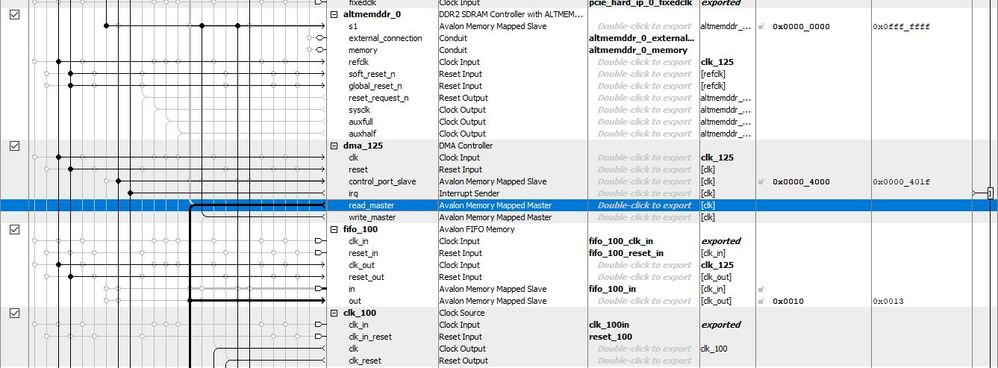

Thank you for your answer. What is wrong with my design? I want to transfer 100 Msps 14 bit ADC continuous data to DDR2 SDRAM using DMA. Is there any issue with the Qsys design below? Anybody please take me out of this hell because I am about to freak out!!

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page