- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

Hi,

I am now working on the SPI in Qsys for a cyclone iv device, I found a problem for the SPI in continually transmission, here is the details.

->The SPI clock is set to 50MHz.

->The software is quite simple:

/***********************************/

for(j=0;j<len;j++)

{while(((IORD_ALTERA_AVALON_SPI_STATUS(SPI_0_BASE))&0x0040)!=0x0040);

IOWR_ALTERA_AVALON_SPI_TXDATA(SPI_0_BASE,*(pBuf+j));

}

/***********************************/

->The purpose is to transmit a lot of data in pBuf as soon as possible.

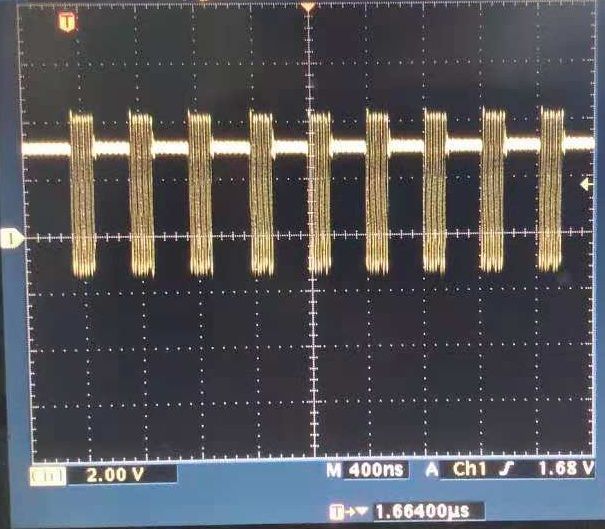

However, I check the SPI clk in oscilloscope, the rate of clk is right as 50MHz, but after one byte(8 bit) have been transmite, there is a 'gap' about 300 ns with no clk output before the next byte transmitted.

->

The 'gap' will make the the SPI data rate reduced much , I want to know what causes it, hope somebody can help me to improve it.

Thank you.

Link copiado

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

That GAP of time is taking about 15 clock cycle(300/20). I think some delay should be expected when you are using IP API in NIOS core and not directly going through custom RTL. When sending command or reading back its status register, it would take some clock cycles in the process,esp in the Qsys interconnect (between master and slave). Also, by looking at the description https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug_embedded_ip.pdf, pg37 SPI core, it is designed to transfer single data word at a time and not support for continuous writing data to SPI slave.

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

@GNg

Thank you very much.

It seems that the CPU takes a very long time to read the SPI register, (The clk of the system is 100MHz, about 10ns).

Will it better if I using a custom RTL and transfer data into it through the Avalon Memory Mapped Master?

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

When you can control directly IP interface , it should greatly reduce the time between transfers.

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

Thank you, I will try it later and give a feedback.

Best regards.

- Subscrever fonte RSS

- Marcar tópico como novo

- Marcar tópico como lido

- Flutuar este Tópico para o utilizador atual

- Marcador

- Subscrever

- Página amigável para impressora