- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I am currently designing an FPGA system that would receive data through a Triple Speed Ethernet protocol and store the data into a SDRAM via the help of a controller.

My Hardware Platform (Qsys) involves two mSGDMAs connecting the Ethernet IP to the SDRAM controller, for rx and tx. I also have an On-chip memory (not for purposes of descriptor memory) which is not connected to the Ethernet IP or the mSGDMAs.

My NIOS BSP linker system has all the memory modules on the on-chip memory except for the heap and stack, which are allocated to the SDRAM controller. I am running the simple socket example, which connects to the ethernet (only when stack or heap are placed in the SDRAM).

My question is how do I know where in the SDRAM to allocate the socket receive buffer. I want to utilize most of the SDRAM space for the data, but I am also aware that some addresses are used for the TCP/IP initialization.

How would I know where my data from the ethernet is being stored (if it's at being stored in the SDRAM) without overwriting previously stored data?

Thank you very much for your help.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear MShro1,

Thank you for using this Intel Community.

You are able to know where your data from Ethernet is being stored by your mSGDMA configuration. In other word, based on your configuration in the mSGDMA (e.g: where to Read and Write data from) should tell you where is the data located in the SDRAM.

Regards,

NAli1

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello NAli1_Intel,

Thank you very much for your reply and the Intel Support. Much appreciated.

A quick follow up on your reply: I am having a little difficulty in finding the exact address of the mSGDMA read/write in the simple socket example shipped with NIOS II (Quartus version 18). I do note that the altera_avalon_tse.c file does contain the initialization and set up for the tx and rx mSGDMAs, but I am unable to find the exact address.

Would appreciate your help.

Thanks once again.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear MShro1,

Please accept my apology on the delay in response as we are on public holidays in my region.

Please allow me some time to look into your issue. I shall come back to you with findings. Thank you very much for your patience.

Regards,

NAli1

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear MShro1,

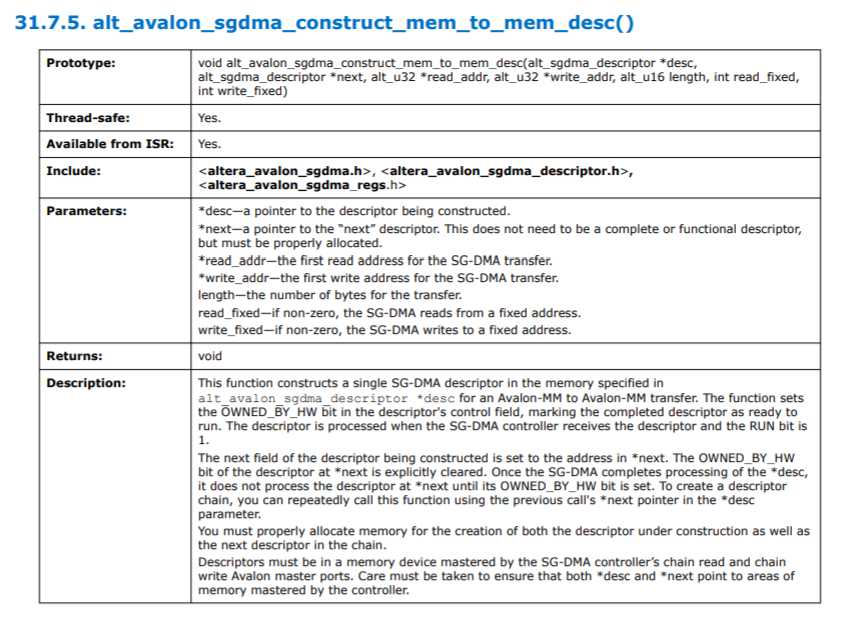

I've generated the simple socket example design and I believed you are referring to this prototype inside the simple socket design which is located inside altera_avalon_sgdma.h file.

I found this handbook which have more details information about the SGDMA controller core in Chapter 31 (page 372) which may be helpful for you 😊 --> https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug_embedded_ip.pdf

Thanks

Regards,

NAli1

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page