- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The truth table:

Input (ABCD) Output

0000 =>0111111111

0001 => 1011111111

0010 => 1101111111

0011 => 1110111111

......

......

library ieee;

use ieee.std_logic_1164.all;

entity nandg1 is

port(A,B,C,D: in std_logic;

y: out std_logic);

end nandg1;

architecture df of nandg1 is

begin

y<= (a nand b) nand (c nand d);

end df;

library ieee;

use ieee.std_logic_1164.all;

entity notg is

port(x: in std_logic;

xbar: out std_logic);

end notg;

architecture df of notg is

begin

xbar<= not(x);

end df;

library ieee;

use ieee.std_logic_1164.all;

entity nandg is

port(A,B,C,D: in std_logic;

Y0,y1,y2,y3,y4,y5,y6,y7,y8,y9: out std_logic);

end nandg;

Architecture df of nandg is

component notg

port (x : in std_logic; xbar : out std_logic);

end component;

component nandg1

port (a,b,c,d : in std_logic ; y : out std_logic);

end component;

signal abar,ain,bbar,bin,cbar,cin,dbar,din: std_logic;

begin

A1: NOTG port map (A,Abar);

A2: NOTG port map (Abar,Ain);

B1: NOTG port map (B,Bbar);

B2: NOTG port map (Bbar,Bin);

C1: NOTG port map (C,Cbar);

C2: NOTG port map (Cbar,Cin);

D1: NOTG port map (D,Dbar);

D2: NOTG port map (Dbar,Din);

L0: NANDG1 port map (Abar,bbar,cbar,dbar,y0);

L1: NANDG1 port map (Ain,bbar,cbar,dbar,y1);

L2: NANDG1 port map (Ain,bin,cbar,dbar,y2);

L3: NANDG1 port map (Ain,bin,cbar,dbar,y3);

L4: NANDG1 port map (Abar,bbar,cin,dbar,y4);

L5: NANDG1 port map (Ain,bbar,cin,dbar,y5);

L6: NANDG1 port map (Abar,bin,cin,dbar,y6);

L7: NANDG1 port map (Ain,bin,cin,dbar,y7);

L8: NANDG1 port map (Abar,bbar,cbar,din,y8);

L9: NANDG1 port map (Ain,bbar,cbar,din,y9);

end df;

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Have you implemented 4input NAND gate in entity nandg1?

y<= (a nand b) nand (c nand d);

should be like y<= (a nand b) or (c nand d);

Also check portmap L2.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Mr. Raj I did the amendment but the outputs still dose not meet the truth table.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Does the gate do what you expect when simulating? What is your expectation of the output and where do you think the simulation of one gate is wrong?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Change the 4-input NAND implementation as it is incorrect. Use the following and then check your BCD to Decimal ckt.

library ieee;

use ieee.std_logic_1164.all;

entity nandg1 is

port(A,B,C,D: in std_logic;

y: out std_logic);

end nandg1;

architecture df of nandg1 is

begin

--y<= (a nand b) nand (c nand d);

y <= not (a and b and c and d);

end df;

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ab4,

The changes proposed in my previous post should work. Which also communicated in private forum message.

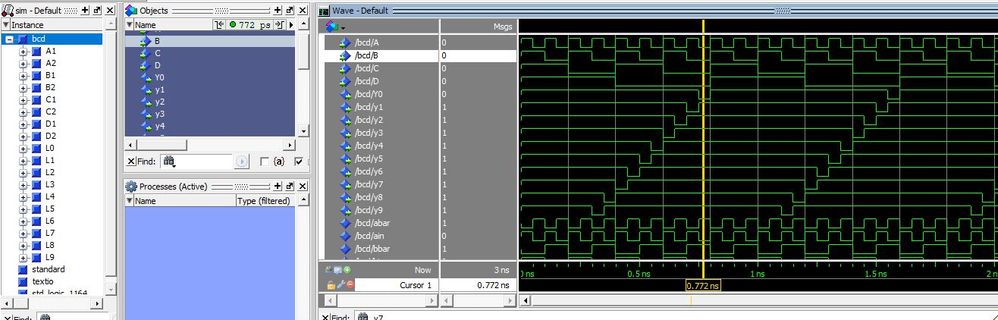

Attaching the simulation output for forum users.

you can copy past the code from my post or from Abe post and try.

Regards

Anand

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page