- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I am developing a project where NIOS II needs to replaced with NIOSV processor. When my design was having NIOS II as CPU, I was running the software code through External SDRAM on the Cyclone IV E Kit(EP4CE40F23C8). It's working fine with NIOS II. Able to run the software program.

Now, when I replaced the NIOS II processor with the NIOSV processor, I am not getting the expected results. I am trying to print a Simple "Hello World" code through the NIOSV processor with the same configuration of design. Almost all BSP settings are same for NIOSV processor as of the NIOS II. Still not getting the results.

When running the NIOSV from On-Chip-Ram, everything works as expected, but when I try to run the NIOSV through external SDRAM, the code does not gets executed as expected.

I want to inquire that if we can run the NIOSV processor through external SDRAM or not ?

Please note that I am not talking here about booting the NIOSV. I am simply running the software image through RiscFree IDE software on the external SDRAM of the board.

Regards,

Himanshu

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Himanshu,

Greetings and welcome to Intel's Forum.

May I know does RiscFree IDE report any Run Configuration failure? By saying execute the code, you mean using RiscFree IDE to download ELF into SDRAM right?

I will get back to you with more information on whether RiscFree IDE supports running software code on external SDRAM.

Thank you.

Regards,

Kelly Jialin, GOH

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Q :May I know does RiscFree IDE report any Run Configuration failure? By saying execute the code, you mean using RiscFree IDE to download ELF into SDRAM right?

A: Yes execute the code means using RiscFree IDE to download ELF into SDRAM, you got it right. And also the RiscFree IDE does not report any Run Configuration failure. There is no problem in downloading the ELF, it works fine up to this point. But my code does get executed as I expect a "Hello World" print as soon as the ELF is loaded, but no success.

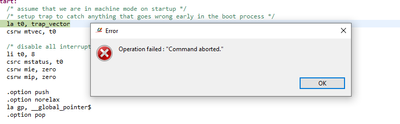

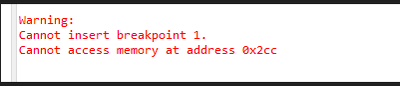

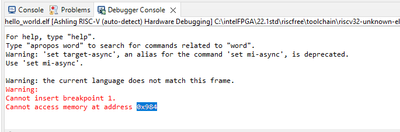

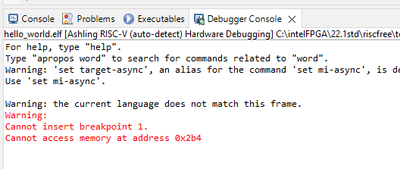

Also I tried today to run the ELF in Debug mode, to verify where the NIOSV is getting stuck. On running through Debug Mode, it prompted me to Error : Operation failed : "Command Aborted". Below are the snapshots of error and warnings of Debugger console.

It seems that ELF is loaded successfully into SDRAM, but when trying to read the code from a particular address, it is getting stucked due to unknown reasons.

Any help regarding this could be appreciated. Thanks !!

Also the Debugger Console shows the warning : "Cannot access memory at address 0x2cc" - To which I want to make sure that is NIOSV processor capable to run through the external SDRAM ? If yes, It would be great if I can get a reference design to run NIOSV Code through external SDRAM.

Thanks in advance !!

Best Regards,

Himanshu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Himanshu,

Unfortunately, we do not have a design example for External SDRAM running on NIOS V for your reference.

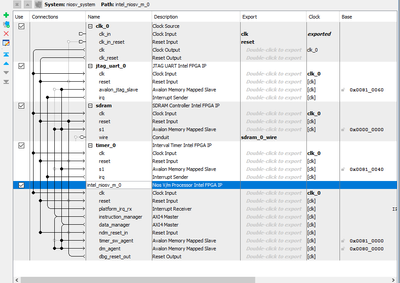

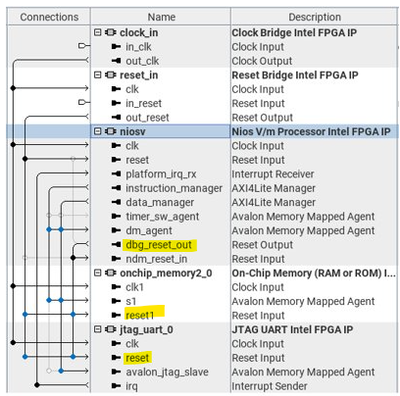

Also, may you check whether the Debug Module reset for NIOS V is connected to the external SDRAM? I will attach a picture of an example for this qsys connection.

Thank you and looking forward to your feedback.

Thank you.

Regards,

Kelly

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

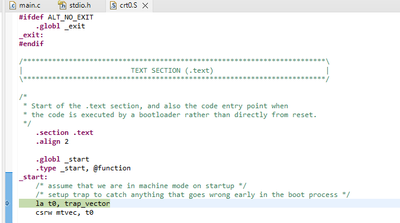

I have verified that the Debug Module reset for NIOSV is connected to the external SDRAM. Please have a look at the below image for my QSYS configuration.

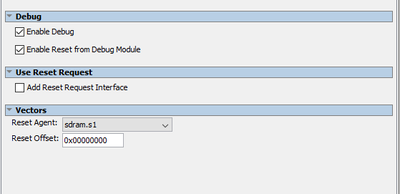

NIOSV configurations:-

With the above configuration, The NIOSV Code is able to get downloaded into SDRAM without RUN configuration failure in normal mode. But, still it gives me the same pop up error while running the ELF in Debug Mode. Error : Operation failed : "Command Aborted".

Debugger Console warning : "Cannot access memory at address 0x984"

Can you please elaborate in detail for the root cause of such issue ? I am again asking just to confirm that can we run NIOSV through external SDRAM ? If yes, then we can debug further with the hardware design perspective.

Thankyou for the co-operation. Looking forward for your response!!

Regards,

Himanshu.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thank you for the information provided. Running NIOS V through external SDRAM should be possible.

Could you try to make the connection between "dbg_reset_out" to "ndm_reset_in" ? I will attach a screenshot on this qsys connection.

Also, could you try to use niosv-download command to try downloading elf to run the application and lowering the JTAG frequency to 6Mhz to check whether is it a RiscFree issue.

Thank you,

Regards,

Kelly

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Attached below is a screenshot of the qsys connection between "dbg_reset_out" to "ndm_reset_in" for your reference. You may connect it as of below to the NIOS V ndm_reset_in , external sdram and jtag's reset.

Thank you and looking forward to your feedback after trying the debugging steps.

Regards,

Kelly

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I have tried to make connection between "dbg_reset_out" to "ndm_reset_in" and also connected it to external sdram and jtag's reset.

With this configuration I again recompiled the design as well as build the software project. But still facing the same issue as I mentioned before. So this did not work out for me. I have attached the snap shot of QSYS system below for your reference.

Also I tried to download the ELF through "niosv-download command" but is doesn't make any differences as well. Lowering the JTAG Frequency to 6MHz also does not work out. So I am stuck at this point to debug further.

I tried to normally do write/read operations in the SDRAM. On-Chip-Ram was used as program memory for this. While doing so, it has been noted that I am able to do 16 bits of write/read transfers successfully. But not able to perform 32-bits of data transfers. May be this can be a issue while reading the ELF stored in the external SDRAM. I will look into this further from my end. But please share your suggestions as well.

Can you please share the PLL configurations for External SDRAM Part No : W9816G6IH ( WinBond ) which has been used on the Cyclone IV E FPGA. What is the minimum clock frequency that needs to be given to SDRAM and also at what phase shift ?

Besides that you can also suggest any fitter assignments which are required for external SDRAM in the QSF file.

Looking forward to hear from you !!!

Regards,

Himanshu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

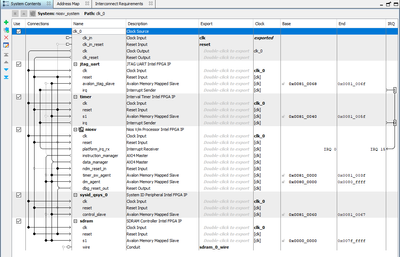

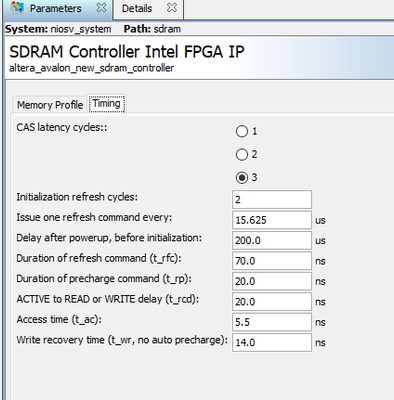

Below is the snap shot of my SDRAM Controller IP configurations. Please have a look and verify if the configurations are correct for Cyclone IV E (EP4CE40F23C8).

Regards,

Himanshu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Himanshu,

Like you, I've been looking for a way to use SDRAM together with the NIOS V. I came across your above post where you shared a Platform Designer screenshot of your system featuring a NIOS V and the SDRAM Controller Intel FPGA IP. I was wondering how you managed to have access to this controller, since it seems this IP is no longer supported on Quartus 23.1. Which version of Quartus do you use?

Thanks in advance for your help.

Best regards

Vincent

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Vincent,

I know that SDRAM Controller IP is no more supported in the latest Quartus Versions. But I would like to inform you that I have the .TCL file that will generate source of SDRAM Controller IP and it's path is added in the user_components.ipx file.(IP_IPX_PATH variable in System Environment) The .TCL will show the SDRAM Controller IP in the QSYS system. It is an older version of SDRAM Controller IP which I am using.

The SDRAM Controller IP, which I am using is from older Quartus 18.x version. To use in the latest Quartus Versions, we need to add the .TCL file in the IP_IPX_PATH variable which have file user_components.ipx.

You can ask INTEL to provide the TCL of the SDRAM Controller IP,

Regards,

Himanshu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Himanshu,

Thanks for your quick reply! I managed to import the .TCL from a previous version. Now I can find the SDRAM Controller IP in QSYS again, but unfortunately, it has no port interfaces. Did you face the same issue, and do you have any idea how I could fix it?

Best regards

Vincent

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Himanshu,

Could you send me a screenshot of the OpenOCD error logs for me to investigate further.

Thank you.

Kelly

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I would like to tell inform you that I am not using the OpenOCD Debugging option from the RiscFree IDE. Instead I am using "Ashling RISCV (auto-detect) hardware debugging option.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Also I would like to mention some related information regarding the issues. The SDRAM consists 16 bit data bus while the data bus of NIOSV bus is 32 bits. Although the tool should be able to manage both the interfaces on its own, but to verify I created another simple design where I used On-Chip-Ram as program memory with 16 bits data width. Now my NIOSV code should work with 16 bit On-Chip-Ram but somehow I faced the same issue which I was facing while using external SDRAM as program memory. The NIOSV ELF gets loaded successfully without Run Failure but does not get executed. While running through Debug("Ashling RISCV (auto-detect) hardware debugging option), I faced the similar issues as I was facing for external SDRAM. The Debugger console shows the warning, "Cannot Access memory at address 0x2b4".

I am attaching the design here for your reference. Please have a look and give your feedback !!

Can NIOSV run with 16 bit On-Chip-Ram. If yes, then why it is resulting in such kind of errors. Only if I change the data width of On-Chip-Ram to 32 bits, everything works fine. But with 16 bit, it is having issues while accessing the code. I think similar issues were there with SDRAM as the data bus of SDRAM is 16 bits.

Please find a solution regarding this. Thanks !!

Regards,

Himanshu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kelly,

I've also been trying to run a Nios V system on a DE10-Lite board (MAX 10 device). I implemented a very simple Hello World project. Everything goes fine when I use the default on-board clock (50 MHz) and the on-chip memory. But, like Himanshu, the system fails to run when using the SDRAM instead of the on-chip memory. The SDRAM requires a PLL for both overclocking (100 MHz) and appropriate timing, so I simply used the same PLL and configuration as for a Nios II project.

Then, I noticed that the Nios V system does not work with a 100 MHz PLL (using on-chip ram only). When configuring the PLL at 50 MHz, everything works fine again (still with on-chip ram only).

Did I miss something while configuring my system, or is there an issue with overclocking the Nios V?

Below is a screenshot of my Platform Designer system for the Nios V configuration.

Best regards

Vincent

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Vincent,

I would like to advice you to add a Avalon MM Pipeline Bridge IP between SDRAM Controller and NIOSV Processor. By doing this you would be able to run software from SDRAM. Below is the configuration of Avalon MM Pipeline Bridge for your reference.

The MASTER Interface of Avalon MM Pipeline Bridge IP must be connected to SDRAM Controller IP and the SLAVE Interface of Avalon MM Pipeline Bridge IP must be connected to NIOSV Processor.

I hope by doing the above change, you will be able to run your software through SDRAM.

Best Regards,

Himanshu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Himanshu,

Thanks for your help. I will try it as soon as I receive a reply from Intel regarding the use of a PLL to overclock the NIOS V. The SDRAM on the DE10-Lite board requires at least a 100 MHz clock to run properly, so the whole system needs to be overclocked. NIOS II works perfectly well at 100 MHz, but it seems there is an issue with overclocking the NIOS V, or maybe (probably) I'm missing something.

Thanks again

Best regards

Vincent

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Himanshu,

This message to inform you, and everyone in the Intel/Terasic community who might be interested, that I managed to implement a NIOS V using the SDRAM on a DE10-Lite board. A few things need to be carefully considered though if you want the system to work.

First, it seems the NIOS V is unable to run at 100 MHz on the DE10-Lite board (while the NIOS II has no problems at 100 MHz). The timing analysis revealed that the maximum frequency is slightly above 95 MHz (maybe Intel people could confirm or otherwise indicate how to improve the NIOS V top frequency on that board). So, I lowered the speed down to 90 MHz (using the altpll IP). By lowering the frequency, I feared the SDRAM module wouldn't work properly since the manufacturer recommends higher frequencies, but it seems to be robust against frequency changes.

Second, you need to select at least the Performance (High-effort - increases runtime) optimization mode in the Compiler Settings. In Balanced mode, the system seems to fail reaching the required timing performance.

Normally, by doing this, you're in business...!

I would also like to add that I experienced some strange behaviours on Ashling RiscFree IDE. First, sometimes the program fails to updated when I want to run a new version. Say for instance, I first run a simple 'Hello World' and then I want to add new instructions, the simple 'Hello World' keeps on running (even when terminating the program properly from the console). I have to restart the whole download process over, and sometimes even need to reset the system before the new app version is taken into account. Any idea where this issue might come from?

Best regards

Vincent

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for the design, we will check the design and get back to you.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page