- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I'm a beginner with Nios II platform designer. I was using an example project from Intel built for Cyclone 10 GX board using Quartus 17.1. It was working fine.

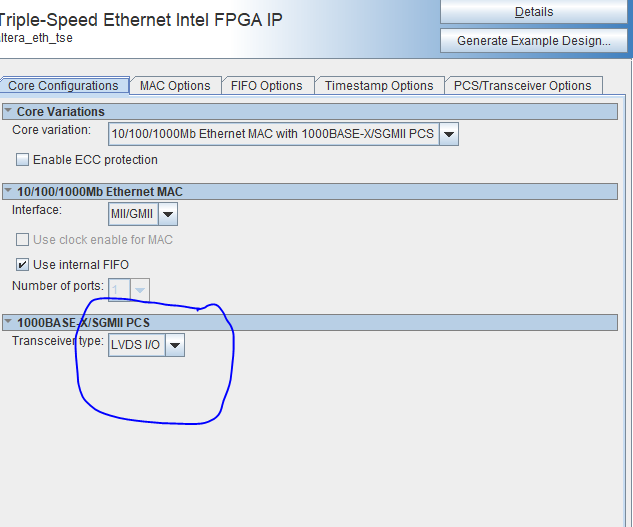

As I need to integrate this design into a main project that was built using Quartus 18.1, I upgraded all the IP in my platform design to 18.1 which resulted in the following error.

“Error(18694): The reference clock on PLL "sss_qsys_inst|tse_0_tse|tse_mac|i_lvdsio_rx_0|core|arch_inst|internal_pll.pll_inst|altera_lvds_core20_iopll", which feeds an Altera LVDS SERDES IP instance, is not driven by a dedicated reference clock pin from the same bank. Use a dedicated reference clock pin to guarantee meeting the LVDS SERDES IP max data rate specification.”

I understand that it got something to do with the Intel's revision of Quartus 18.1. Kindly let me know how to proceed further with the Triple Speed Ethernet IP in this scenario

Update 1 : I've attached both the project files. First one is for 17.1 and it works. The next one is altered by 18.1 and it's not working.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Yes, this error was during fitter in the compilation process. I'm using the same design as the one used for 17.1, in fact I loaded the design into 18.1 platform designer and just upgraded the IP, everything else remains the same.

It's the Simple socket server example built for Cyclone 10 GX, I found somewhere in the Intel FPGA site.

Please find the attached zip for the project that works with 17.1 and also the altered one from 17.1 to accommodate 18.1. I've added the files to the main query.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Please let me know if you any updates on this issue.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

What that error means is that you have to use Dedicated clock inputs that drive the PLL. FPGAs have Dedicated PLL inputs and dedicated PLL outputs which you need to use in order to maximize the data rate when using specific protocols such as LVDS. These Pins for the C10GX are :

PIN_N23/24

PIN_R23/24

PIN_U23/24

PIN_W23/24

Use these pins to feed the Ref Clk input to PLLs and this will solve the issue.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

In the Cyclone 10 GX board, I can see those 4 pins are used for SFP, PCIE, USB and FMC. In the example design that worked for 17.1, the PIN_AB16 was used as the refclk, but i's not working for 18.1

PIN_N23/24 is dedicated for SFP,

PIN_R23/24 is dedicated for PCIE,

PIN_U23/24 is dedicated for USB,

PIN_W23/24 is dedicated for FMC.

I think in this case, either Intel has to change the layout of the board to let us use one of those four dedicated pins, or revert back the TSE IP core the way it was in 17.1

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Rama ,

Sorry for very late response ;

Can you check in the board device used is Engineering sample not the Production one ?

Thank you ,

Regards,

Sree

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It is a Cyclone 10 GX evaluation board(10CX220Y) bought through distribution. So I guess that makes it a production board.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Could you compare the production board schematic and and the design 17.1 pin map ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

we are experiencing the same issue with the Cyclone 10GX evaluation board. If I understood correctly this seems to be a hardware bug of the evaluation board, as there is no LVDS clock connected to the bank 2L where the Ethernet Core is connected to?

The clock "C10_REFCLK1p" (n) which is used in the simple socket example uses another bank and the clock "C10_REFCLK2p" (n) is connected to pins G23 & F23, which don't support LVDS.

According to the following post, the LVDS SERDES IP requires a LVDS clock on the same bank.

Best Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello , sorry for very late reply

Would it possible to find the revision of the eval board and cross verify ?

Each Rev there will be different pin out and changes in the schematic design as well.

Thank you ,

Regards,

Sree

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sure.

10CX220YF780E5G board saying 100-0321329-A1 Rev A

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We also have the same revision: 100-0321329-A1 Rev A.

Best Regards

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page