- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I am trying to use the NIOS II SIMPLE Socket Server design template to write data from a file to the SDRAM. Right now we are facing issue to fit the design along with our algorithm on to Cyclone V GT board. The resources are cramming up. Will the usage of hard external memory interface can improve our situation in any aspect? Under what circumstances to we get to see the benefits of the same? If possible, can I get any reference design that uses this hard memory controller?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

Your understanding is correct. Using the hard memory controller has the advantage in FPGA resource usage because it is hardend block.

When you create the IP via Megawizard GUI you will be asked whether to create the example design or not. if you click yes example design will be generated automatically.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

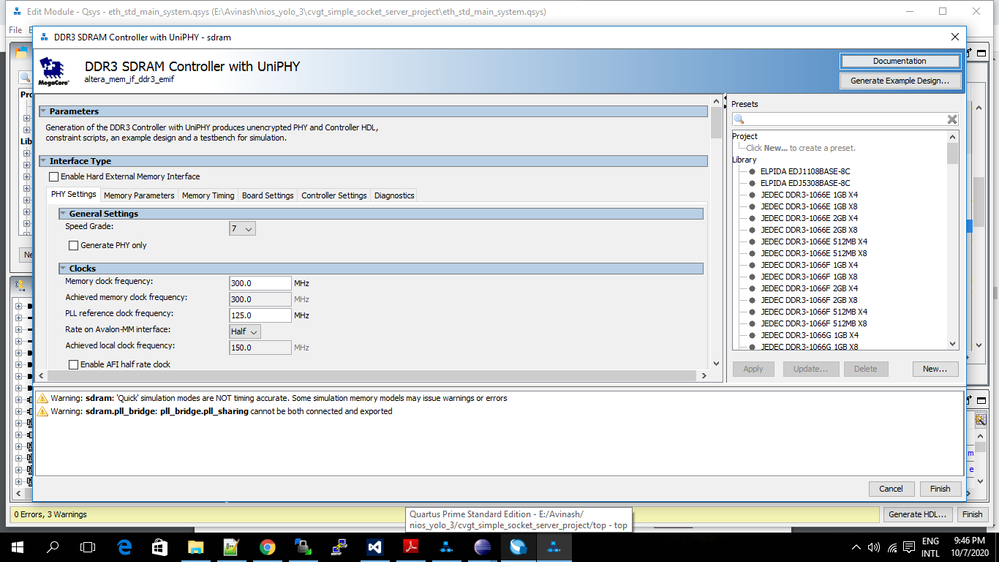

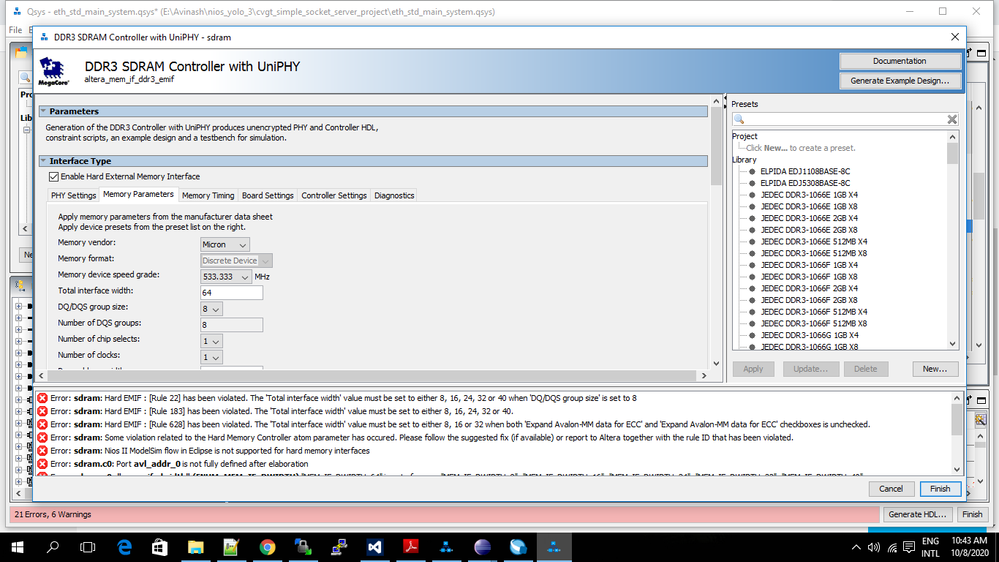

Thank you for your response @yoichiK_intel . Whenever I am enabling "Enable Hard External Memory Interface" in the DDR3 SDRAM Controller with UniPHY in the platform designer, I am getting a series of errors as shown in the screenshot. I feel that the default settings are going for a toss once I have enabled the option. I am looking for a reference design from Intel that has used this hard external memory interface so that I can get a better idea.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page