- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hardware board: AGFB023R25A Ethernet Card + 100G QSFP28 DAC cable external loopback.

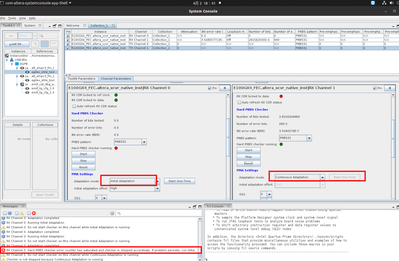

Problem: Use the System Debugginng Toolkits com-altera-systemconsole-app-shell to debug 53.125Gbps performance. Serial Loopback is ok ( ber=0 and inject error bits is tested ok). But BER is wrong when set to external loopback ( The message is "Hard PRBS checker error counter has saturated and checker is stopped accordingly..., But the lock status is True and ber is showing continuely when I turn the adaptation mode to continous Adaptation).

Question: Please help me check the Serdes of FPGA setting. Now I can't see any of serdes setting on this console toolkits.

Note: hardware is ok, cable is ok , test operation procedure is OK. The BER result is OK when I tested 2 days before.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jason,

How long is your external loopback module? Firstly I'd like to suggest you try to add a bit TX EQ see if the link would be better first, just in the lower part of the Tx channel parameters.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi there,

I wanted to check if you have any further questions or concerns. If not, I will go ahead and mark this issue as resolved.

Additionally, we would greatly appreciate it if you could take a moment to fill out our survey. Your feedback is valuable to us and helps us improve our support quality.

Thank you for your time and cooperation.

Best regards,

WZ

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page