- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

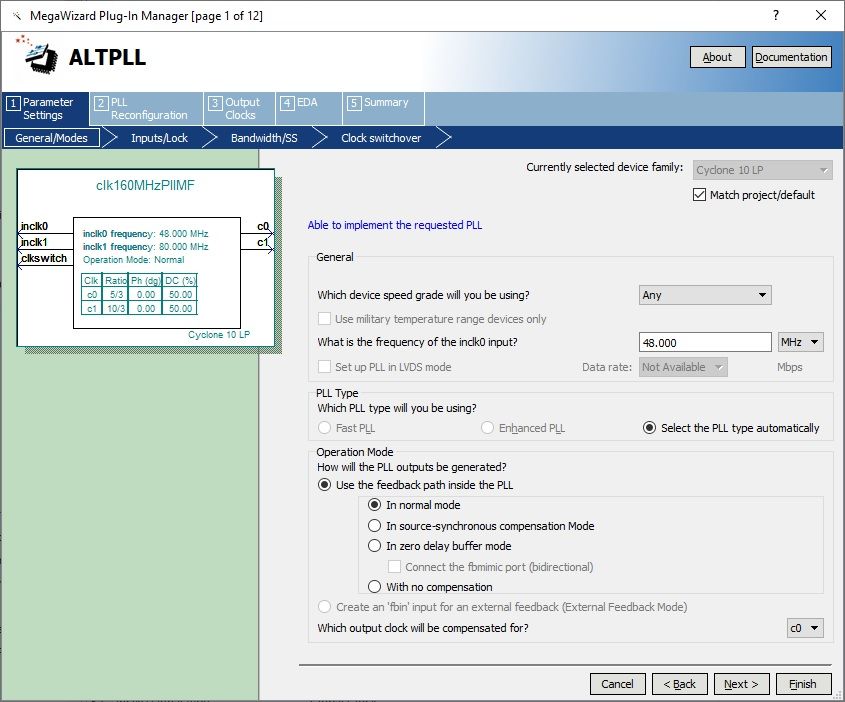

I am using the ALTPLL to generate a 80MHz clock from a 48MHz clock. This is fine. Later when an independent clean 80MHz clock is available

I am switching over to this clock by using the clock switchover function in ALTPLL. When I switchover I get a very high

frequency clock that my 100MHz scope is unable to display correctly. How does the ALTPLL adjust the PFD divisor when I do the switchover.

Why am not getting an 80MHz clock. Am I missing something.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @User15891149574421405910 You will need to perform a dynamic reconfiguration if you want to keep the same 80Mhz when you are switching ref clock from 48Mhz --> 80Mhz.

Normally, the usage model is that....

For redundancy purposes, you have 2 ref clock of the same frequency + automatic switchover.

For clock sources originate from multiple cards on the backplane, requiring a system-controlled switchover between frequencies of operation (e.g. manual switchover + dynamic reconfiguration).

Hope this answers your questions.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Chin,

Thanks for the clarifications. As a feedback if this point is captured in the documentation as well as the ALTPLL IP Catalog software it would be great.

As a simple workaround to the dynamic configuration I am spoofing the 48MHz clock as 80MHz in the IP Catalog. i.e I mention inClk0 as 80MHz but give a 48MHz. This is a temporary arrangement until I get the clean 80MHz inclk1 in my application. It is working fine. But are there any design pitfalls in the PLL that would give random problems in field?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @User15891149574421405910 I am not sure what random problems you are referring to...but i guess it depends on your application. As a rule of thumb, as long as the PLL is locked, the output is reliable.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page