- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

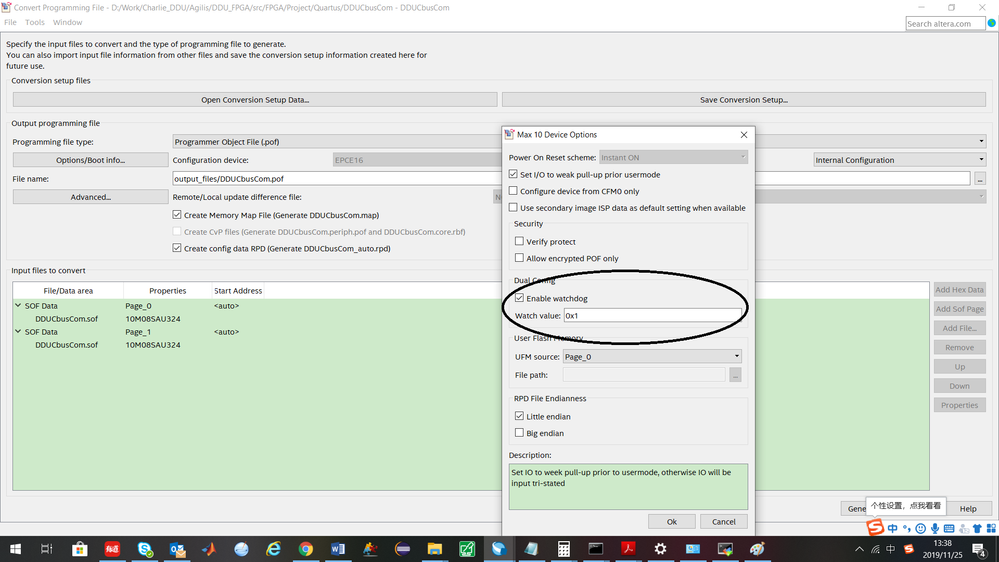

FPGA communicates with another FPGA with PHY chip. Normally(watchdog enable checkbox not checked), the PHY link led is always off when communication is good. While after I enble watchdog for dual-config(watchdog enable checkbox checked) and set watchdog value to any value, the link led will be on for about 2 seconds and return to be off. This will also be repeated after dozens of seconds. Why? How will I use the watchdog for dual-config? I didn't run remote update after power-up and the FPGA just run application firmware(just ethernet communication with another FPGA using PHY chip).

Attached file is my fpga code for the dual-config.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Sorry. It should be 0xFFF.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It's the same when I set timer to 0xFFF.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

May I know if you are able to read msm_cs whenever PHY communication is down?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Maybe I could and I can have a try if you need.

Anyway, I am sure reconfig didn't happen and just PHY comminication goes wrong. I have two PHY communication path with the same phy chip in my master board which communicate with a slave board which also have two PHY path. In th slave board, One phy chip is the same PHY chip with master board, the other phy chip is different But they can communicate well without enabling watchdog. After I enable wathdog,the same phy chip works well while different phy chip will meet problems like what I mentioned.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

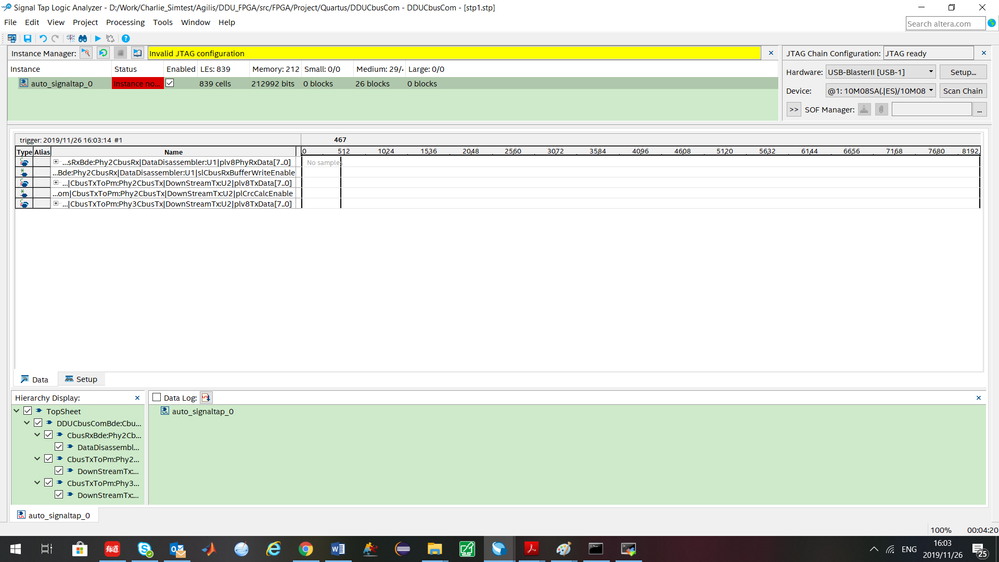

Thanks for the explanation. It looks like something went wrong when you enable the watchdog timer. I think you will need to signalTap into your design to understand what is causing the PHY communication to break down. Cause the working chip does not face any issue and the reset watchdog timer should be working correctly.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, there must be sth wrong with enbale watchdog. But I don't know what's the problem so I ask you about this. After all, the problem only happens when I enable watch dog. I still don't know where should I go and Anything else to recommend to look into? So can heip me to find the problem.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

You need to look into your PHY Communication interface and check why it is breaking down. I don't think that the watchdog timer can cause any issue on this except that watchdog timer times out and cause reconfiguration to happen.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

But only when I enbled the watchdog did problems come, so I think there is sth to do with watchdog. I will go on looking into it and hope you could give me some solutions or comments about this if you have further findings. I would also hope could you please ask about this issue with your colleagues and maybe get some ideas. Thanks very much!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I will need to further understand your PHY link and how it work on your design to understand what is actually happening to further understand what is happening. The reason is that watchdog timer will cause the Max 10 device to reconfigure if it is not reset correctly.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

This phenomenon is cause by the Max 10 being reconfigured. I would suspect that the reset watchdog timer is not being set. Not sure if you have a way to confirm that your state machine is executing the writing into the reset watchdog timer?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, @JohnT_Intel

I have another question, could you please help me to solve it? This question is emergency, so I hope it can be resolved as soon as possible. Thanks very much!

The issue is:

Each of our product will have a unique serial number which is 4 bytes long, like 0x"0F0F0F0F". The number will be written into FPGA in our product. But the serial number will be modified for different products when they leave factory. FPGA in the product will read this serial numer when the product operates in customer's place. How can I realize this?

My initial idea is like below:

( I make a file whose content can be edited. The file is edited with 4 bytes's serial number. Then this file can be downloaded into UFM and FPGA could read the serial number from UFM.

But how will I make such a file that can be edited and be programmed into UFM with Jtag or other ways?)

Besides that, are there any other good ways to realize this function except what I proposed? If not, please tell me how to realize the function I proposed.

Thanks very much!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

If you would like to add unique serial number into UFM then you can only use hex file to incorporate into POF and program into the UFM.

The other method is to use System ID Periphery Core IP (https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug_embedded_ip.pdf Chapter 40) to incorporate the ID for each of your system design.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,@JohnT_Intel

Thanks for your idea.

While there is a problem for us. The serial number will be set by workers in the factory ,then they can only program a file with serial number into FPGA. This will be done independently with the application pof. The worker in factory can't compile FPGA project and they can only do the programming with Jtag. So they just modify the file and download this file directly into UFM. So how will this be realized. Thanks very much!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

May I know if each device will have it's own serial number? The reason is that if you would like to implement different serial number for each pof file will be difficult.

If this is The case then I would recommend you to use On Chip Flash IP to directly program the bitstream using rpd file (raw programming file) then this will make you easier to modify the rpd file as it is a raw binary file and you may refer to .map file to determine where you can use to store the serial number. This will be more harder to implement as you need to create a design where you can update the UFM directly.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,@JohnT (Intel)

Each device will have different serial number. So I don't know how to realize this.

rpd can't be programmed by Jtag and Is this possible that I can modify .pof directly to edit the serial number inside this file?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

This is not possible if you are using POF file as it contain checksum for CRC checking.

May I know if you are able to update the UFM with the serial number after the POF is programmed? The reason is that I would recommend you to use JTAG Master and On Chip Flash IP to update the UFM with Serial Number so that it will be easier to be implemented.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,@JohnT (Intel)

I can update the UFM with the serial number after the POF is programmed. It is OK. Then how to realize later?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

You can create a simple JTAG to Avalon Master IP with On Chip Flash IP design to program to Max 10 device and use Quartus System Console to write into the specific UFM address to store the Serial Number.

Attach is the design example that I created for Max 10 Development kit.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,@JohnT (Intel)

Thanks for your idea. While The problem is that workers in factory can’t compile. They just can program a file into FPGA.

They will edit a file with different serial number to each product and then program the file into FPGA.

Is there a method that I can edit a file and then directly program the file into FPGA without compiling. Thanks!

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page