- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We evaluate the performance of the PCIe IP with Avalon MM interface on the Arria V FPGA. We only achieve a data rate of 1400*10^9 bytes per second which is less than written in the "PCI Express High Performance Reference Design

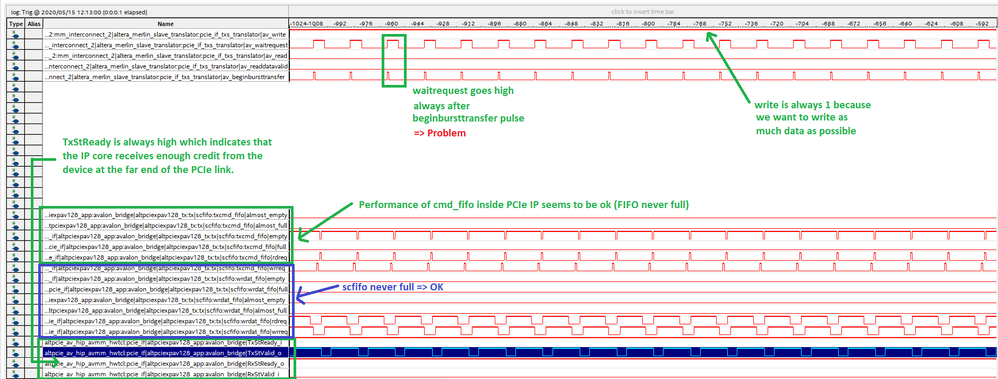

" document in table 10 (1784 MB per second). Using signal tap we observed that the Avalon MM waitrequest signals changes to 1 after the beginbursttransfer signal pulse during every burst.

To find the reason for this worse performance we used signal tap to monitor the fifo full and empty signals of the cmd_fifo and the wrdat_fifo inside the PCIe IP. Both full signals are never 1 so the FIFO see to be ok.

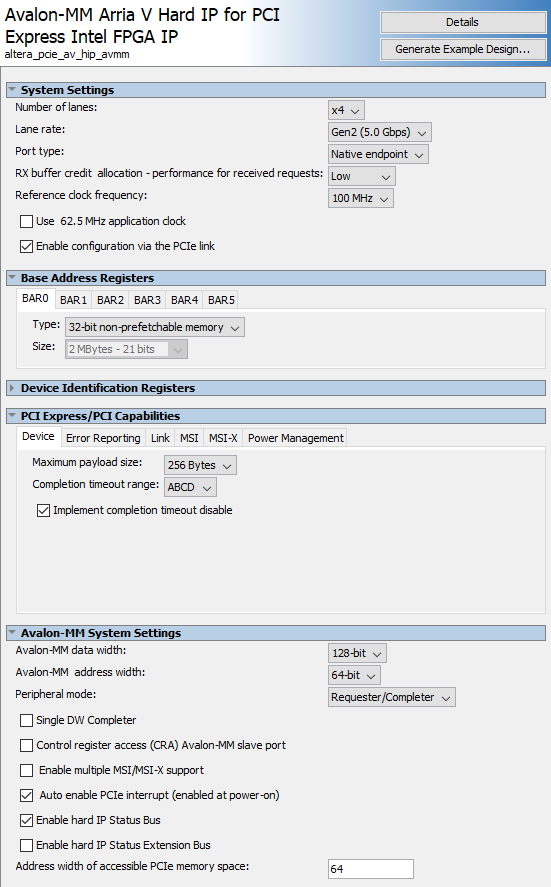

As suggested on page 18 of AN-456-2.4 we looked at the TxStReady to find out whether the PCIe core does not receive enough credit but this seems not to be the case. Do you have any advice how to solve this problem? Here the parameters of the PCIe IP:

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Really apology for the late reply, kindly let me know you are using custom board or development board.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We are using custom hardware.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ,

To understand the issue more , kindly let me know which wait request you are mentioning , for Avalon MM there are more than one waitrequest signal. so kindly let me know which specific waitquest signal you are mentioning.

If you can let me know with respect to the block diagram mentioned , that will be great.

Page no:140

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug-01105-1_6.pdf

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Signal TxsWaitRequest_o in Figure 7–34 on page no 139

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ,

I was doing my research and found out that the behavior is expected.

May I know why you are asserting the being burst transfer for a periodically.

If you are asserting the above signal, slave will make sure the burstcout, write and byteenable signals are stable in the bus.

So that is why slave is asserting the signal. Once wait request is de-asserted data will start to transfer. But if you see your waveform you are asserting the being burst transfer, periodically.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

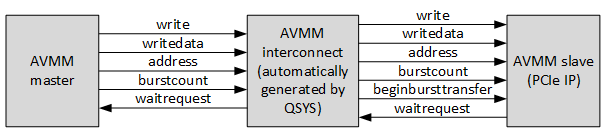

See the attached image for the setup. We wrote an Avalon MM master using VHDL. It is connected to an Arria V Avalon MM PCIe IP though an AVMM interconnect that is automatically generated by QSYS. The befinbursttransfer signal you mentioned above is a signal between the automatically generated interconnect and the instantiated PCIe IP. We do not have any control over that signal.

The AVMM master asserts the write signal in every clock cycle because we want to write in every clock cycle. This is however not possible because the AVMM slave (PCIe IP) asserts waitrequest whenever we start a new burst. What is the reason for this poor performance?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ,

Taking conversation in to private

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page