- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

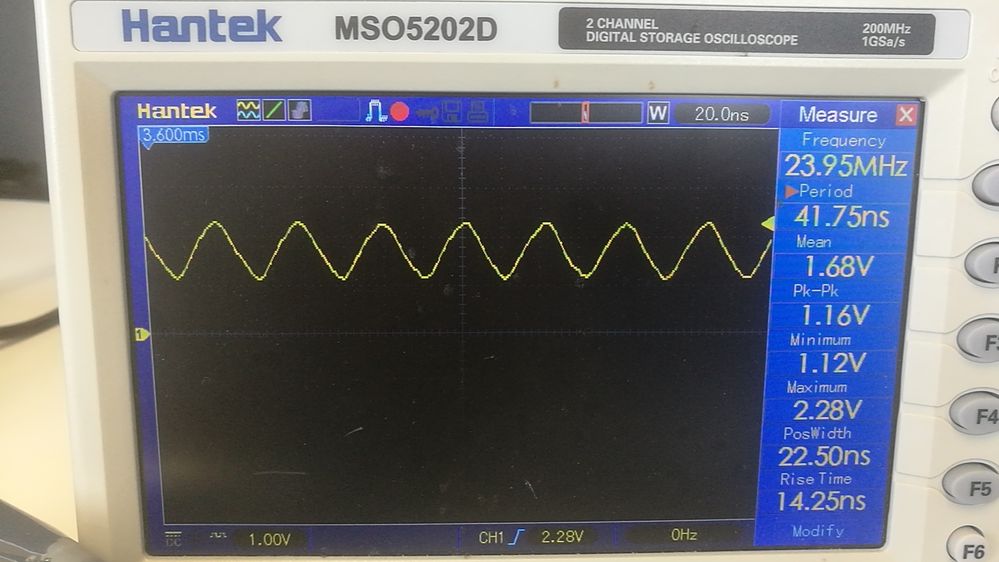

I tried to use general IO to generate a clock for other ICs. This generated clock is from the PLL which is fed in with a crystal oscillator. When I measured this clock at the output pin, I found that the frequency is correct as I expected, but the voltage is not correct.

This pin is configured as LVCMOS-3.3v, so the Voh/Vol should around 3.2v/0.1v, but from this image below, the Max/Min voltage is 2.28v/1.12v. It has an above 1v DC offset which makes trouble for other ICs who use this clock.

My question is how to reduce this DC offset to make the IO generated clock meet the LVCMOS standard.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Is there any update from your end? I will need to close this case in 3 days if there is not respond from you.

Thank you.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Are you using Intel FPGAs? May I know which device and what is your OPN?

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Is there any update from your end? I will need to close this case in 3 days if there is not respond from you.

Thank you.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page