- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I am working on a project where I use:

1) 1-port (or 2-port) on-chip RAM (Block RAM) with data width 128b and size of 360960B, running at 160MHz.

2) A process for capturing camera data (DCMI interface) running at 26.67MHz and storing 752x480 monochrome images into the BRAM (by 16px chunks, when needed) using the port A.

3) A process for VGA output (to HDMI transceiver ADV7513 on DE10-Nano) running at 40MHz, loading the image by 16px chunks from the BRAM (when needed) using the port B.

4) Clock 160MHz is generated by PLL from the 50MHz input clock, frequencies 40MHz (160/4) and 26.67MHz (160/6) are generated from the 160MHz using second PLL.

Everything works fine both with the built-in 1-port RAM (Altera Megafunction IP) and with custom inferred 2-port BRAM (using this VHDL code). (I don't use Altera's 2-port RAM because I was not able to get it working with SignalTap, which was complaining about size limit of 553 blocks.)

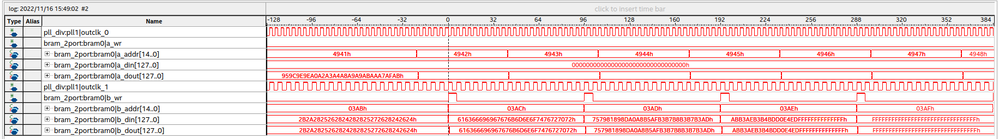

The SignalTap recording of the ports of the custom 2-port BRAM is in the next image:

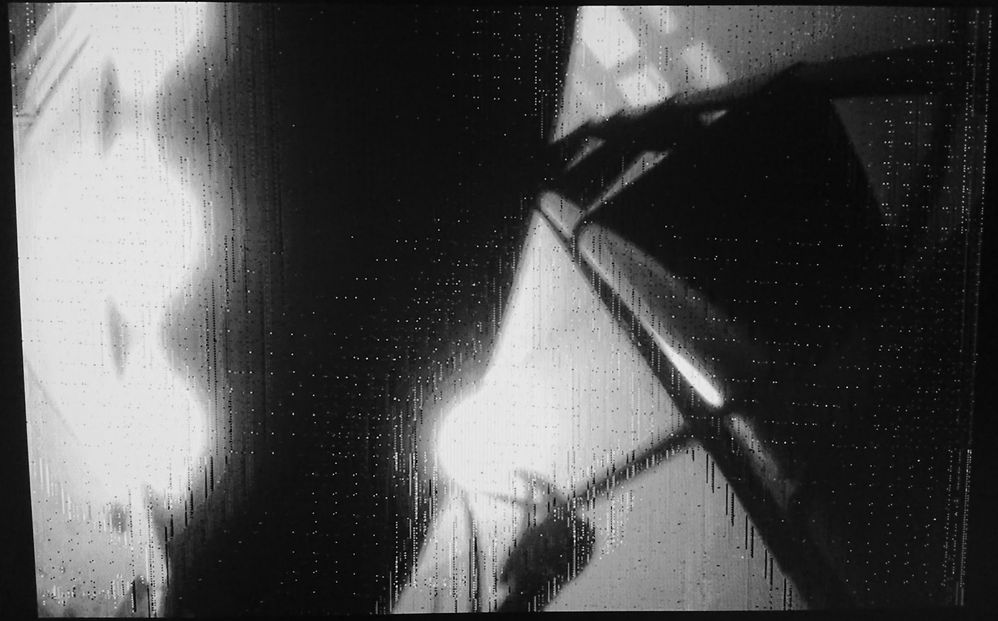

And the resulting image on the HDMI output looks as expected:

Because I would like to use also HPS, I tried to add soc_system.qip generated by the Platform Designer. I used the working DDR configuration from the GHRD, removed all GPIOs, peripherals, kept only Clock source IP component (connected to the 50MHz clock) and the HPS IP block to have a minimal configuration of the HPS.

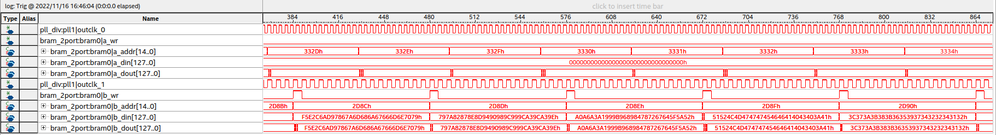

But for some reason when the soc_system component in the top module is initialized, the BlockRAM read (dout) port starts behaving weird (even it is completely separate from the soc_system component):

And it results in the following artifacts in the HDMI output:

I really don't understand why this is happening. I tried to feed the clock source with the derived 40MHz clock (I thought it could be a timing issue) but it behaves the same. The same problem happens with the Altera's 1-port RAM. When I comment out the system_soc component and remove the qip file from the project, it starts working correctly again..

Thanks for any suggestions on what I am doing wrong and how this can be solved.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Since there is a duplicate case @https://community.intel.com/t5/FPGA-SoC-And-CPLD-Boards-And/Cyclone-V-BlockRAM-read-port-stops-working-when-HPS-SoC-added-to/m-p/1431294#M23488

We will communicate everything through that case instead of here.

Best Regards,

Richard Tan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

This thread will be transition to the community support. If you have a new question, Please login to ‘https://supporttickets.intel.com’, view details of the desire request, and post a feed/response within the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you on your follow-up questions.

Thank you.

Best Regards,

Richard Tan

p/s: If any answer from the community or Intel Support are helpful, please feel free to give best answer or rate 9/10 survey.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page