- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

So my system has a cyclone V with a nios processor.

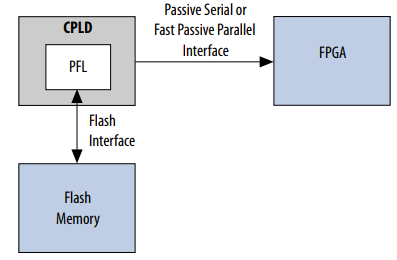

This FPGA is configured using CPLD MAX 10.

The configuration mode for cyclone V is passive serial ( PS ).

The nios and FPGA can boot when pointing both reset vector and exception vector on the OCRAM. But now the Nios application image is bigger than the maximum OCRAM size and the solution is to run the application on DDR.

How can I achieve that ?

PS: The CPLD is connected to a parallel flash , and the cyclone V is also connected to the parallel flash but the configuration mode is passive serial not passive parallel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Can try Nios II Processor Booting from CFI Flash if using Cyclone V check this https://www.intel.com/content/www/us/en/docs/programmable/683689/current/processor-booting-from-cfi-flash.html

Then probably can set the configuration scheme and mode to passive serial as The PFL IP core allows you to configure the FPGA in passive serial (PS) or fast passive parallel (FPP) scheme. Check this https://www.intel.com/content/www/us/en/docs/programmable/683698/21-1-19-1-0/supported-schemes-and-features.html

Pointing both reset vector and exception vector to Parallel Flash and External RAM (DDR) respectively.

Here are some references may be helpful to you:

https://community.intel.com/t5/FPGA-Wiki/Nios-II-Booting-From-CFI/ta-p/735490

https://malt.zendesk.com/hc/ja/articles/900006257703-Nios-II-Boot-Option-CFI-Flash-

Best Regards,

Sheng

p/s: If any answer from community or Intel support are helpful, please feel free to mark as solution and give Kudos.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Can try Nios II Processor Booting from CFI Flash if using Cyclone V check this https://www.intel.com/content/www/us/en/docs/programmable/683689/current/processor-booting-from-cfi-flash.html

Then probably can set the configuration scheme and mode to passive serial as The PFL IP core allows you to configure the FPGA in passive serial (PS) or fast passive parallel (FPP) scheme. Check this https://www.intel.com/content/www/us/en/docs/programmable/683698/21-1-19-1-0/supported-schemes-and-features.html

Pointing both reset vector and exception vector to Parallel Flash and External RAM (DDR) respectively.

Here are some references may be helpful to you:

https://community.intel.com/t5/FPGA-Wiki/Nios-II-Booting-From-CFI/ta-p/735490

https://malt.zendesk.com/hc/ja/articles/900006257703-Nios-II-Boot-Option-CFI-Flash-

Best Regards,

Sheng

p/s: If any answer from community or Intel support are helpful, please feel free to mark as solution and give Kudos.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page