- Marquer comme nouveau

- Marquer

- S'abonner

- Sourdine

- S'abonner au fil RSS

- Surligner

- Imprimer

- Signaler un contenu inapproprié

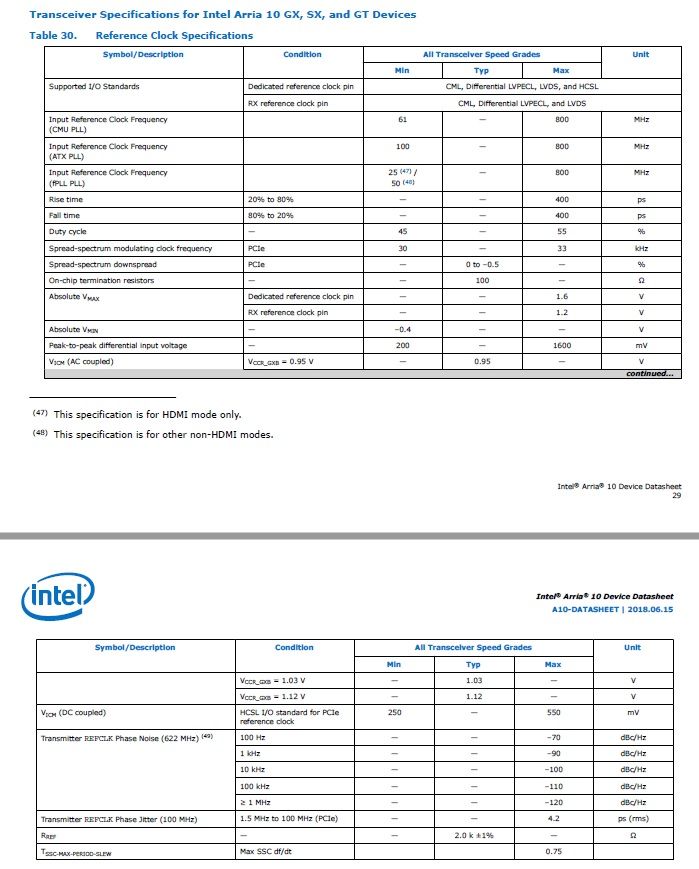

I have a design which includes a PCIe endpoint, a 10GE MAC/PHY and a triple-speed ethernet MAC/PHY. Tool-generated pin constraints force the reference clock I/O types to be HCSL for the PCIe, LVDS for the 10GE, and CML for the triple-speed ethernet. Per the A10 datasheet, input electrical specs for all three I/O types are pretty much the same:

The HCSL must be DC-coupled, and I have a driver specifically for that. But other than that, it appears that LVDS, differential LVPECL, and CML drivers will all work equally well.

So why the three different I/O type constraints? Can I drive them all with the same technology (other than the DC-coupled HCSL)?

Lien copié

- Marquer comme nouveau

- Marquer

- S'abonner

- Sourdine

- S'abonner au fil RSS

- Surligner

- Imprimer

- Signaler un contenu inapproprié

- Marquer comme nouveau

- Marquer

- S'abonner

- Sourdine

- S'abonner au fil RSS

- Surligner

- Imprimer

- Signaler un contenu inapproprié

Yes, I understand that the PCIe reference clock input requires a DC-coupled HCSL driver (I actually wrote that in my original post), and I know that CML and LVPECL use AC coupling (I wrote that as well). And I don't see how those facts support the conclusion that [I] "need to follow the protocol specification".

And it does not address my questions:

- Why are the reference clock I/O constraints different even though the I/O cells are all the same?

- Can I drive all of the AC-coupled reference clock with the same driver type (any driver that meets the stated specifications for the reference clock inputs), and if not, why?

- Marquer comme nouveau

- Marquer

- S'abonner

- Sourdine

- S'abonner au fil RSS

- Surligner

- Imprimer

- Signaler un contenu inapproprié

The FPGA is flexible for you to choose which IO standard to use, each standard has its own advantages and disadvantages and it run at a range of difference input/output voltage level.

The supported IO standards of reference clock for Arria 10 are CML, Differential LVPECL, LVDS and HCSL. And yes, you can use either one for difference application. For example, the 10GE, TSE IP and XCVR PHY can use the same IO standard for reference clock in your design.

Regards -SK

- Marquer comme nouveau

- Marquer

- S'abonner

- Sourdine

- S'abonner au fil RSS

- Surligner

- Imprimer

- Signaler un contenu inapproprié

Hi,

Below is of the follow up question:

- One is for a triple-speed Ethernet MAC/PHY and requires a CML clock; I don’t have a convenient way to create a CML driver; can I drive this ‘CML’ input with an LVDS driver?

Answer:

No, If you configure the IO standard as CML in FPGA, this is NOT recommend to drive this input with an LVDS driver.

If I understand it correctly, your oscillator output connected to FPGA Ethernet PHY reference clock is of LVDS IO standard. If yes, then you may change the IO standard assignment for the FPGA Ethernet PHY reference clock from CML to LVDS using assignment editor. The FPGA Ethernet PHY reference clock supports LVDS IO standard as well.

Regards -SK Lim

Regards -SK Lim

- S'abonner au fil RSS

- Marquer le sujet comme nouveau

- Marquer le sujet comme lu

- Placer ce Sujet en tête de liste pour l'utilisateur actuel

- Marquer

- S'abonner

- Page imprimable