- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi team

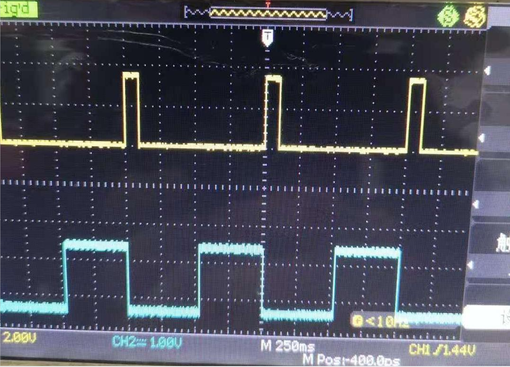

I had debug GE 1588 V2 in my board is Slave , and Third party equipment is Master。The 1PPS signal output from my board is sync to the 1PPS signal output from the Master equipment, but threre are something wrong, the slave 1PPS Falling edge sync to the Rising edge of the master equipment 1PPS.

How can i make the Rising edge sync to Rising edge between the slave and the master

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hello anybody

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Did I put the post in the wrong board?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Mark,

I am afraid we won't be able to provide assistance to you on the offset adjustment.

This is due to Intel FPGA IP does not implement event messaging protocol layer, but only provide basic hardware capability (i.e. timestamping) in implementing 1588 protocol

User logic will manage PTP messaging and corresponding offset adjustments. My understanding is the offset algorithm is typically managed by high level software stack.

Another suggestion to you is perhaps you can check back with your test equipment vendor to see if they are able to provide you further guidance or any setting that can fine tune in the test equipment or not.

Thanks.

Regards,

dlim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Another suggestion is you can also try play around with the sync mode of the "TOD sync IP" page 13, table 14

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Deshi

Thanks for your guidance , I will try to play around with the sync mode and test with another test equipment.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI Mark,

Sorry, pls ignore my suggestion on the TOD sync IP - sync mode setting.

I clarified further with Intel internal team.

- The TOD sync IP is just good to sync up the master TOD and slave TOD IP within the FPGA internally.

- It won't help to sync the offset between PTP slave device (FPGA) and PTP master device (your test equipment)

Ultimately user is still expected to build your own design algorithm to adjust the PTP offset btw master and slave device yourself. From Intel FPGA Ethernet IP side, we only provide the timestamp info but not the offset adjustment solution

I dig through some reference design and found below example design that comes with PTP offset adjustment software stack solution.

- https://rocketboards.org/foswiki/Projects/Stratix10SoCDesignExampleFor10GbeWithIEEE1588PTPCapability

- I am not sure how helpful is it but feel free to check it out

Thanks.

Regards,

dlim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Deshi

Thank you for your help and support about the 1588 PTP

Thanks.

Regards,

mark

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page