- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

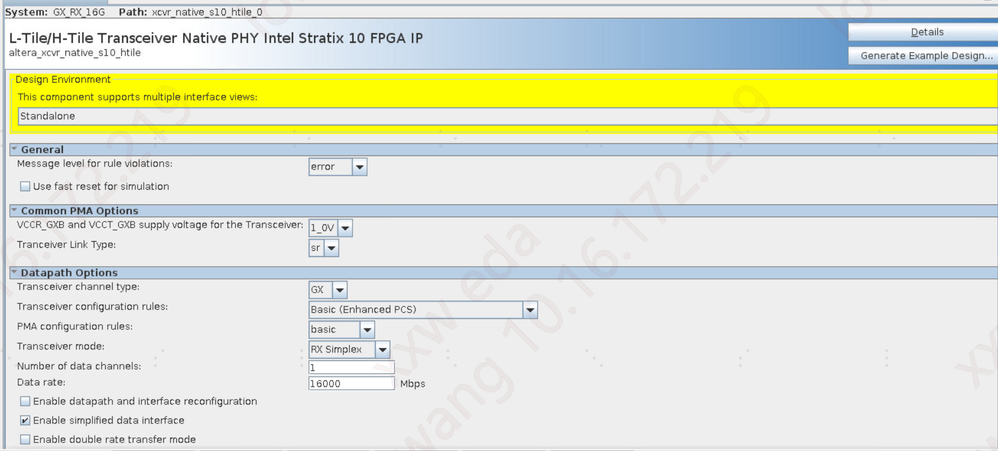

Use L-Tile/H-Tile Transceiver Native PHY Intel Stratix 10 FPGA IP. The "datapath Options” and Common PMA Options” configurations are shown in the attached pictures.Using PRBS to test the bit error rate at the speed of 16Gpbs, it is found that there is a high bit error rate.

I used the default values for "RXPMA" and "Enhance PCS" and "PCS-Core Interface" and "Analog PMA Settings" and "Dynamic Reconfiguration" in this PHY IP. Do I need to change the parameters in these options? What parameters need to be changed?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

You might need to change the Analog PMA Settings. You can try with example design first.

Thank you,

Kshitij Goel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Have you tried it? Is the issue resolved?

Thank you,

Kshitij Goel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

As we do not receive any response from you on the previous answer that we have provided. Please login to ‘https://supporttickets.intel.com’, view details of the desire request, and post a response within the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you on your follow-up questions.

Thank you,

Kshitij Goel

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page