- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The PCIe Hard IP placement always starts at bottom transceiver block.

T: Top

B: Bottom

So please assign the pcie refclk pin to the Bottom location REFCLK_GXBL1C_CHB (B)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks, that is what I will do! Is there anywhere specific in the documentation that I could have found that information?

Is REFCLK_GXBL1C_CHB required (REFCLK_GXBL1C_CHT wouldn't work) or is it just preferred (easier fitting or something like that)?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I repost the reply.

You can download and refer to the Device pin-out file of '10CX085' from below link:

https://www.intel.com/content/www/us/en/support/programmable/support-resources/devices/lit-dp.html

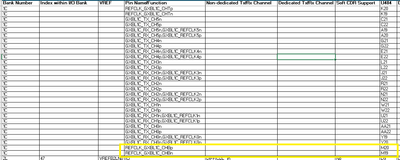

It is required to use REFCLK_GXBL1C_CHB.

Inside the pin out file:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You can download and refer to the Device pin-out file of '10CX085' from below link:

https://www.intel.com/content/www/us/en/support/programmable/support-resources/devices/lit-dp.html

It is required to use REFCLK_GXBL1C_CHB.

Inside the pin out file:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Did you post some images? I can't tell for certain, but it looks like the images aren't showing up in the post.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page