- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

In a project done using Arria V FPGA (5AGXFB1HF35I3), I'm using an IP (LPM_MULT) with the following properties:

- dataa and datab input width - 16bit

- result output width - 32bit

- Signed

- Two clock pipelines

- With clken and aclr

I have a component with 2 multipliers and 2 adders (implementing a FIR), and since this component is instantiated many times across my design (along with other, different components that use DSP blocks), I want to save up as many DSP blocks as possible.

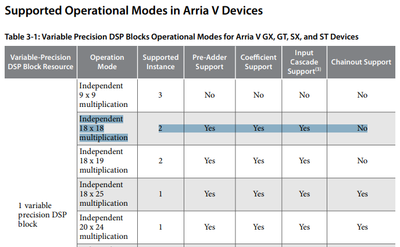

According to the Arria V handbook, 2 multipliers can fit in 1 DSP block:

According to the Quartus 18.1 compilation report I see that each multiplier uses 1 DSP block, instead of 2 multipliers using 1 DSP block. This causes Quartus to use all the available 920 DSP blocks.

Note: something strange that I see is that while for some instantiations of the FIR component there are 2 DSP blocks (instead of 1), for others no DSP blocks are implemented at all. Could be some kind of weird merge?

This is an issue for me since:

- According to calculations I made, Quartus should have used far less DSP blocks. This was assuming 2 multipliers fit into 1 DSP block.

- I need to see if my design converges (resource-wise), since my design will be implemented inside another design (that uses some DSP blocks). Therefore I need to know if there are spare DSP blocks in my design (as in my calculations).

Thank you.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Have you used the suggested IP cores for Arria® V variable precision DSP blocks implementation?

https://www.intel.com/content/www/us/en/docs/programmable/683213/current/operational-modes.html

Thank you

Kshitij Goel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

If you're talking about what they're saying here:

The following Intel® Quartus® Prime IP cores are supported for the Arria® V variable precision DSP blocks implementation:

- LPM_MULT

- ALTERA_MULT_ADD

- ALTMULT_COMPLEX

- ALTMEMMULT

Then yes, I've used the LPM_MULT IP.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Does no one know?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Please share your project to reproduce and analyze the issue.

Thank you

Kshitij Goel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Please share your project to reproduce and analyze the issue.

Thank you

Kshitij Goel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

As we do not receive any response from you to the previous question that I have provided. This thread will be transitioned to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread.

Thank you

Kshitij Goel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Sorry for not replying.

Unfortunately I am unable to share the project since it is work related and I am not allowed to do that.

Are there some requirements for merging multipliers into DSP blocks? Perhaps I am missing something.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page