- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

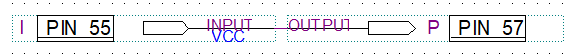

For testing how to use input in EPM240T100C5 physically, I set up the following buffer .bfd :

Supposedly, when I connect the available VCC to PIN 55, the PIN 57 will be HIGH. Else, PIN 57 should be low.

However, once I programmed the board, the PIN 57 is HIGH all the time.

I then tested using other gates like AND gate instead of directly connecting input and output together. Still, the output is always HIGH.

How should I properly use input in physical circuit? Thanks!

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Question closed.

What a careless mistake. I forgot to connect the ground. It should look something like this.

https://www.youtube.com/watch?v=f6j700YDQfs

Basically, it is VCC => push button => ground, and in between push button and ground, just take a wire input to the input pin.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page