- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

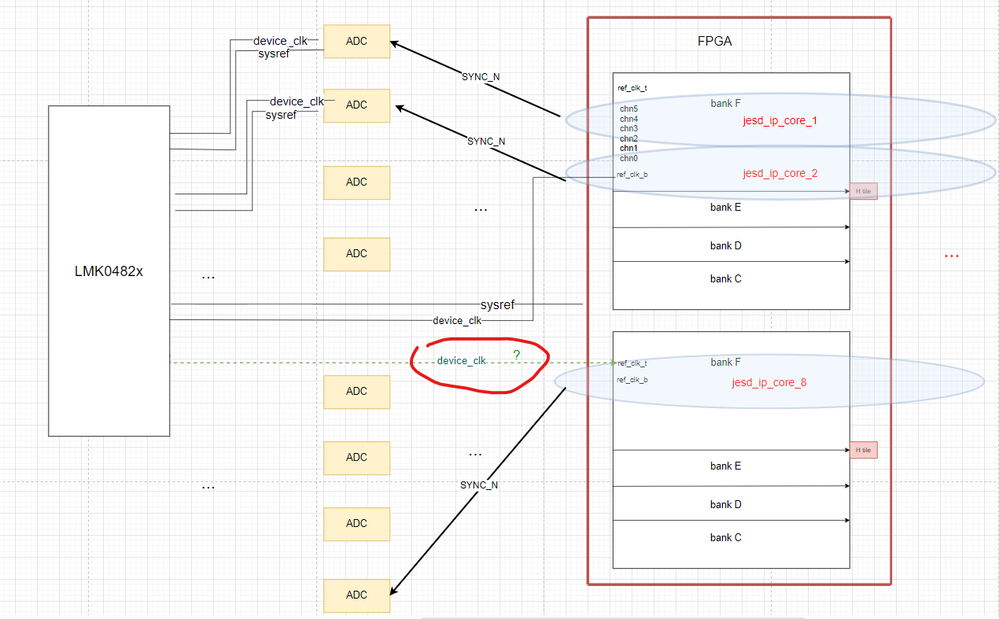

Hello everyone, I have encountered some issues in designing an FPGA solution for receiving ADC data. The FPGA I am using is stratix10-1SX110HN2F43I2VG, which has two tiles, with each tile having 4 banks. Each bank has 6 channels and two reference clock inputs.

I need to use the JESD204B interface to synchronize the inputs of 8 ADC chips. I have checked the IP core guideline, which tells me that I need to instantiate 8 IP cores for the 8 links. I plan to use 4 lanes for each IP core, requiring a total of 32 channels.

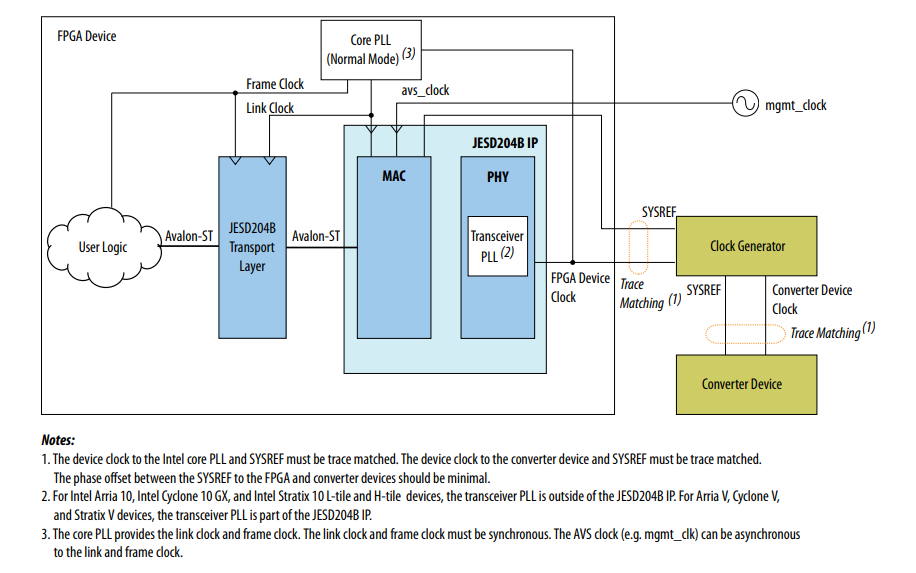

I intend to use the first H tile for 24 channels, accommodating 6 IP cores, while the remaining 2 IP cores will be placed in the second H tile. I also plan to distribute the device clock output from the LMK0482X chip to the reference clock of the first H tile, and I will also connect this clock to the PLL core to generate the frame clock and link clock.

I plan to share the sysref signal connected to the FPGA to the 8 IP cores. Assign it to common IO pins ,because it's a low-speed signal .

1.I want to know if the 8 IP cores in the two tiles can share the reference clock connected to the first H tile ? If not, I may need to connect another device clock to the reference clock of the second H tile. These two clocks will be used for the 6 IP cores in the first tile and the 2 IP cores in the second tile.

2.Another issue is that the LMK0482X chip can only output a maximum of 7 sets of device clocks and sysref signals, but my design seems to require 9 sets of device clocks and sysref signals or more. How should I design it more reasonably?

- Tags:

- JESD204B

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have solved this problem. I used a clock buffer chip to replicate multiple sets of clocks.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Allen,

Thank you for reaching out.

Just to let you know that Intel has received your support request and currently we are confirming the details with our internal team.

I shall come back to you with findings.

Thank you for your patience.

Best Regards,

ZulsyafiqH_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have solved this problem. I used a clock buffer chip to replicate multiple sets of clocks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Allen,

Apologize for the delayed response as we encounter some technical difficulty.

Glad that your problem is solved, I now transition this thread to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread.

Thank you.

Best Regards,

ZulsyafiqH_Intel

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page