- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have a board with 2 x 10M04DCF256 devices on it. The JTAG chain is wired up serially (TDO from device 1 goes to TDI of device 2). The chain is fully functional. Here is the observed behavior:

- If using Byte Blaster and 2 .pof files in the programmer, the two devices configure normally.

- If using Byte Blaster and loading a single .jbc file (made from two pofs), programming fails (see image below).

- If using quartus_jli, and same .jbc file, programming fails in the same way.

- If using Jam Stapl software (ported onto ARM in our embedded system), programming fails the same way.

- If, however, I generate a .jbc file where either one of the two devices is bypassed, programming succeeds, with all software tools, including our embedded port.

The above behavior is 100% consistent. If I do the same experiments again, I get the same results.

I suspect some sort of issue either with generation of the jbc file, or with the code that plays the jbc file, specifically with a multiple Intel-FPGA device chain.

We have implemented numerous other boards with single devices on the chain, and this always works fine.

So, I am looking for some guidance on how to resolve this issue.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Dpond,

I think this one is known issue (JAM/JBC file generation).

The issue is caused by Quartus Prime update version.

We will update the new KDB for this issue in near future. And this bug is scheduled to be fixed in a future release of the Intel Quartus Prime software.

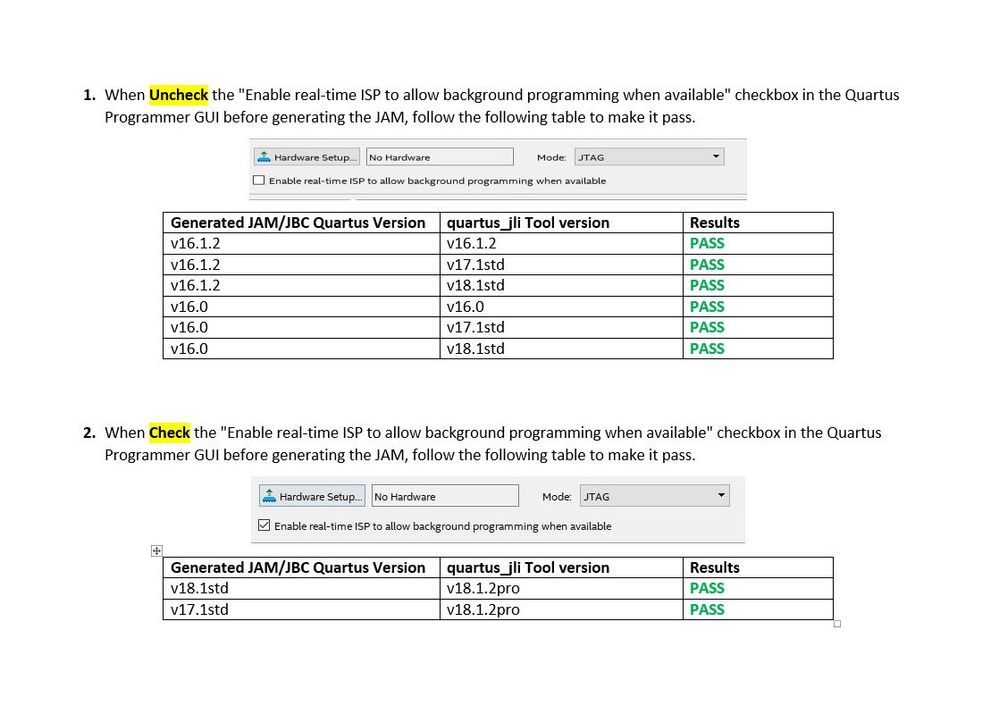

In the meantime, please refer to the attachment picture for workaround:

I hope this will help

Thanks.😉

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Wolfgang,

I am using Quartus version 18.1 Lite. I used your suggestion (check the Enable real-time ISP...) and generated a combined jbc file. The result was successful, now both FPGAs get configured when we execute that .jbc file using altera Stapl code on our embedded system.

Thank you for your help.

-Dan

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page