- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am studying the workings of DDR memory, in particular the recommendations for PCB layout. One of the intel documents (Table 1–24; Page 70) has the following wording: "Propagation delay of clock signal must not be shorter than propagation delay of DSQ signal at every device"

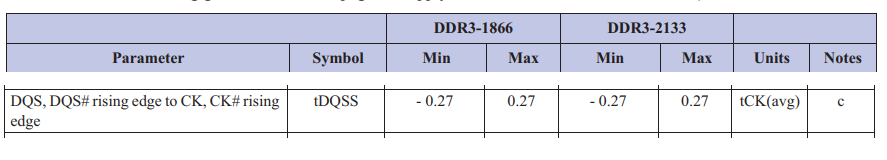

However, if this is compared with the requirements from JEDEC(Registration required for reading,Table 69, page 175):

Where tCK is Average Clock Period = 8ns.

In the JEDEC standard I can clearly see the negative time tdqss relative to the rising edge tCK, which says that the DQS line is shorter. Is Intel(Altera) not DDR compliant or am I missing something?

Link Copied

0 Replies

Reply

Topic Options

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page