- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

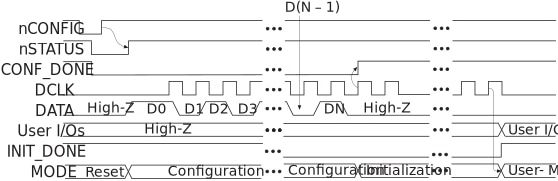

My question is about the Nstatus and ConfDone signals behavior when Nconfig is submitted to perturbations:

Assuming we have a 10kohm pull-up with the 3V3 on Nconfig as suggested by Altera's documentation, and a short but high perturbation occurs forcing Nconfig to less than 1V during a few hundreds nanoseconds, how does an Altera Cyclone IV e react? During this short amount of time, will the Users I/O turn to High Z? is the FPGA going in reset state? How about Nstatus and Confdone signals?

Link Copied

1 Reply

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi LauraC,

If the nCONFIG is driven LOW in short amount of time, the FPGA will go to RESET state.

And the USER I/Os are tri-stated until the device enters user mode.

Thanks.

Regards,

Matt

Reply

Topic Options

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page